# ELECTRICAL SWITCHING STUDIES OF CHALCOGENIDE-BASED ION-CONDUCTING VARIABLE RESISTANCE DEVICES

by

Beth Rose Cook

A thesis

submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Boise State University

May 2011

© 2011

# Beth Rose Cook

# ALL RIGHTS RESERVED

# BOISE STATE UNIVERSITY GRADUATE COLLEGE

# DEFENSE COMMITTEE AND FINAL READING APPROVALS

of the thesis submitted by

# Beth Rose Cook

Thesis Title: Electrical Switching Studies of Chalcogenide-Based Ion-Conducting Variable Resistance Devices

Date of Final Oral Examination: 09 March 2011

The following individuals read and discussed the thesis submitted by student Beth Rose Cook, and they evaluated her presentation and response to questions during the final oral examination. They found that the student passed the final oral examination.

| Kristy A. Campbell, Ph.D.   | Chair, Supervisory Committee  |  |  |

|-----------------------------|-------------------------------|--|--|

| R. Jacob Baker, Ph.D., P.E. | Member, Supervisory Committee |  |  |

| Jim Browning, Ph.D.         | Member, Supervisory Committee |  |  |

The final reading approval of the thesis was granted by Kristy A. Campbell, Ph.D., Chair of the Supervisory Committee. The thesis was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude for the individuals that follow. They have all assisted in the completion of my thesis and master's degree. First, I would thank my advisor Dr. Kris A. Campbell for the opportunity to work in her research group and for the invaluable professional advice she has bestowed upon me. This is in addition to the diligence she has shown in the assistance of the completion of my thesis. I would also like to thank the committee members, Dr. Jim Browning and Dr. R. Jacob Baker, for taking the time to make this thesis possible.

I want to thank the other members of the Campbell group, past and present, for their willingness to assist, instruct and for being a sounding board to bounce ideas off of.

I would like to thank Clay Mayberry, Dr. Arthur Edwards, Dr. Rod Devine, Bill Kemp, and Richard Netzer of the AFRL at Kirtland AFB. Their assistance and discussions were valuable to my understanding of radiation exposure and their kindness made me feel I had always been a part of the group.

I am thankful for members at Micron Technology, such as Dr. John Smythe III and Dr. Scott Sills, for their mentoring and valuable discussions on CBRAM. I would also like to thank Rob Goodwin for providing the SEM and STEM mapping of an ionconducting device.

Finally, I would like to take a moment to thank my family. Without their love and support, I never would have been able to achieve so much.

## ABSTRACT

In this work, ion-conducting devices using layers of chalcogenide materials are explored as potential non-volatile memory devices. This technology is also known in the literature as conductively bridged RAM (CBRAM), programmable metallization cell (PMC), and programmable conductor RAM (PCRAM; not to be confused with the acronym PCRAM as used to denote phase-change memory).

Electrical measurements with five different programming currents at four temperatures have been performed on two-terminal devices comprised of silver with a metal-selenide and germanium-chalcogenide layer. The metal-selenide layer is Sb<sub>2</sub>Se<sub>3</sub>, SnSe, PbSe, In<sub>2</sub>Se<sub>3</sub>, or Ag<sub>2</sub>Se. The germanium-chalcogenide layer is either Ge<sub>2</sub>Se<sub>3</sub> or GeTe. Total ionizing dose radiation effects are also investigated for GeTe/SnSe/Ag and Ge<sub>2</sub>Se<sub>3</sub>/SnSe/Ag devices.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv                                                    |

|------------------------------------------------------------------------|

| ABSTRACTv                                                              |

| LIST OF TABLES ix                                                      |

| LIST OF FIGURES                                                        |

| CHAPTER 1: INTRODUCTION                                                |

| 1.1 Introduction and Motivation1                                       |

| 1.2 Overview of Ion-Conducting Variable Resistance Devices             |

| 1.2.1 Operation of Silver Ion Migration through Chalcogenide Glasses 3 |

| 1.3 Summary of Thesis7                                                 |

| CHAPTER 2 : ION-CONDUCTING DEVICES: MATERIALS AND ELECTRICAL           |

| CHARACTERIZATION METHODOLOGY9                                          |

| 2.1 Introduction                                                       |

| 2.2 Ion-Conducting Two-Terminal Device Layout                          |

| 2.3 Fabrication of Ion-Conducting Two-Terminal Devices                 |

| 2.4 Chalcogenide Film Choices                                          |

| 2.4.1 Metal-Selenide Layer Choices                                     |

| 2.4.2 Germanium-Chalcogenide Layer Choices                             |

| 2.5 Electrical Testing Description16                                   |

| 2.6 Conclusion                                                         |

| CHAPTER 3 : WRITE THRESHOLD VOLTAGE CHARACTERISTICS 19                 |

| 3.1 Introduction                                                       |

| 3.2 Compliance Current and Temperature Effects                         |

| $3.2.1 \text{ Ge}_2\text{Se}_3/\text{Sb}_2\text{Se}_3/\text{Ag}$       |

| $3.2.2 \text{ Ge}_2\text{Se}_3/\text{SnSe}/\text{Ag}$                             | 24 |

|-----------------------------------------------------------------------------------|----|

| 3.2.3 Ge <sub>2</sub> Se <sub>3</sub> / PbSe/Ag                                   | 28 |

| $3.2.4 \text{ Ge}_2\text{Se}_3/\text{Ag}_2\text{Se}/\text{Ag}$                    | 33 |

| $3.2.5 \text{ Ge}_2\text{Se}_3/\text{In}_2\text{Se}_3/\text{Ag}$                  | 36 |

| 3.2.6 GeTe/SnSe/Ag                                                                | 40 |

| 3.3 Comparison of Metal-Selenide Layers                                           | 46 |

| 3.4 Comparison of Germanium-Chalcogenide Layers                                   | 48 |

| 3.5 Conclusion                                                                    | 51 |

| CHAPTER 4 : RESISTANCE CHARACTERISTICS                                            | 52 |

| 4.1 Introduction                                                                  | 52 |

| 4.2 Programming Current and Temperature Effects on Resistance                     | 52 |

| 4.2.1 Stack Ge <sub>2</sub> Se <sub>3</sub> / Sb <sub>2</sub> Se <sub>3</sub> /Ag | 53 |

| 4.2.2 Stack Ge <sub>2</sub> Se <sub>3</sub> / SnSe/Ag                             | 57 |

| 4.2.3 Stack Ge <sub>2</sub> Se <sub>3</sub> / PbSe/ Ag                            | 60 |

| 4.2.4 Stack Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag                | 63 |

| 4.2.5 Stack Ge <sub>2</sub> Se <sub>3</sub> /In <sub>2</sub> Se <sub>3</sub> /Ag  | 67 |

| 4.2.6 Stack GeTe/SnSe/Ag                                                          | 70 |

| 4.3 Comparison of the Metal-Selenide Layered Devices                              | 73 |

| 4.4 Comparison of the Chalcogenide Memory Layered Devices                         | 74 |

| 4.5 Conclusion                                                                    | 75 |

| CHAPTER 5 : TOTAL IONIZING DOSE EFFECTS ON RETENTION AND                          |    |

| PROGRAMMING OF SnSe-BASED DEVICES                                                 | 76 |

| 5.1 Introduction                                                                  | 76 |

| 5.1.1 Device Description                                                          | 78 |

| 5.1.2 Instrument Description                                                      | 78 |

| 5.2 Electrical Testing and Measurements of Total Ionizing Dose Effects on         |    |

| Programmed Devices                                                                | 80 |

|                                                                                   |    |

# LIST OF TABLES

| Table 2.1: Table of the Devices Tested in This Work and Corresponding Target Film                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Thicknesses11                                                                                                                             |

| Table 2.2: Table of Standard Reduction Potentials of Metals from Metal-Selenide Layer                                                     |

| (11)                                                                                                                                      |

| Table 3.1: Average Threshold Voltage Values for Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Device at Five       |

| Different Programming Currents and Four Different Temperatures                                                                            |

| Table 3.2: Typical Voltage Threshold Values for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Devices at Five                                  |

| Different Programming Currents and Four Different Temperatures. (-)                                                                       |

| Represents There Is No Threshold Voltage Due to the Device Already 'ON' 28                                                                |

| Table 3.3: Typical Voltage Threshold Values for Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Device at Five                                   |

| Different Programming Currents and Four Different Temperatures. (-) Signifies                                                             |

| There Was No Threshold Voltage. (*) Signifies Voltage When Compliance                                                                     |

| Current Was Reached                                                                                                                       |

| Table 3.4: Average Threshold Voltage Values for Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag Devices as a                       |

| Function of Compliance Current and Temperature                                                                                            |

| Table 3.5: Typical Threshold Voltage Values for Ge <sub>2</sub> Se <sub>3</sub> /In <sub>2</sub> Se <sub>3</sub> /Ag Device as a Function |

| of Temperature and Programming Compliance Current                                                                                         |

| Table 3.6: Average Threshold Voltage Values for GeTe/SnSe/Ag Devices as a Function                                                        |

| of Programming Current and Temperature. (*) Signifies the Voltage When                                                                    |

| Compliance Current Was Reached. (-) No Threshold Voltage                                                                                  |

| Table 3.7: Typical Voltage Threshold Values for All Metal-Selenide Devices at Five                                                        |

| Different Programming Currents and Four Different Temperatures. (-) No                                                                    |

| Threshold Voltage, (*) Signifies Voltage When Compliance Current Was                                                                      |

| Reached                                                                                                                                   |

| Table 3.8: Activation Energies and Electric Field at $V_{T1}$ Values of Metal-Selenide                                                    |

| Devices                                                                                                                                   |

| Table 3.9: Typical Voltage Threshold Values for GeTe/SnSe/Ag and Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag                     |

|-------------------------------------------------------------------------------------------------------------------------------|

| Devices as a Function of Temperature and Compliance Programming Current.                                                      |

| (*) Signifies the Voltage When Compliance Current Was Reached. (-) No                                                         |

| Threshold Voltage 50                                                                                                          |

| Table 3.10: Activation Energies and Electric Field at $V_{T1}$ of SnSe Devices with Ge <sub>2</sub> Se <sub>3</sub> or        |

| GeTe Memory Layers                                                                                                            |

| Table 4.1: Average Erase and Second Write Resistance Values at 23 °C Pre- and Post-                                           |

| Thermal Exposure of 150 °C for Ge <sub>2</sub> Se <sub>3</sub> / Sb <sub>2</sub> Se <sub>3</sub> /Ag Devices. The Virgin      |

| Devices, Pre- and Post-Thermal Exposure, Had an Initial Resistance of                                                         |

| Approximately $5 \times 10^{11}$ and $3 \times 10^{11} \Omega$ , Respectively                                                 |

| Table 4.2: Average Erase and Write Resistance Values at 23 °C Pre- and Post-Thermal                                           |

| Exposure of 150 °C for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Devices. The Virgin Devices, Pre-                             |

| and Post-Thermal Exposure, Had an Initial Resistance of Approximately $1 \times 10^8$                                         |

| and $5 \times 10^7 \Omega$ , Respectively                                                                                     |

| Table 4.3: Average Erase and Write Resistance Values at 23 °C Pre- and Post-Thermal                                           |

| Exposure for Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Devices. The Virgin Devices, Pre- and Post-                             |

| Thermal Exposure, had an Initial Resistance of Approximately $6 \times 10^6$ and $8 \times 10^6$                              |

| $\Omega$ Respectively                                                                                                         |

| Table 4.4: Average Erase and Write Resistance Values at 23 °C Pre- and Post-Thermal                                           |

| Exposure for Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se <sub>3</sub> /Ag Devices. The Virgin Devices, Pre- and Post- |

| Thermal Exposure, Had an Initial Resistance of Approximately $2x10^{11}$ and                                                  |

| $5 \times 10^{10} \Omega$ , Respectively                                                                                      |

| Table 4.5: Average Erase and Write Resistance Values at 23 °C Pre- and Post-Thermal                                           |

| Exposure for In <sub>2</sub> Se <sub>3</sub> /Ge <sub>2</sub> Se <sub>3</sub> /Ag Devices. The Virgin Devices, Pre- and Post- |

| Thermal Exposure, Had an Initial Resistance of Approximately $3x10^{11}\Omega$ 69                                             |

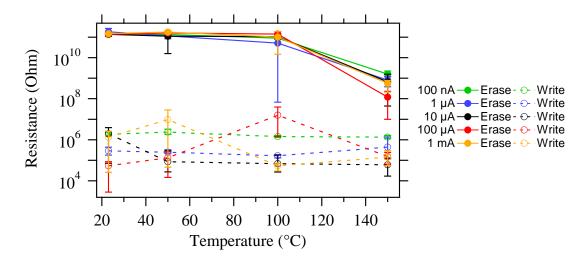

| Table 4.6: Average Erase and Write Resistance Values at 23 °C Pre- and Post-Thermal                                           |

| Exposure for GeTe/SnSe/Ag Devices. The Virgin Devices, Pre- and Post-                                                         |

| Thermal Exposure, Had an Initial Resistance of Approximately $2x10^8$ and $4x10^6$                                            |

| $\Omega$ , Respectively                                                                                                       |

| Table 4.7: Average Second Write Resistance Values from All Temperature Ranges for                    |

|------------------------------------------------------------------------------------------------------|

| the Varying Metal-Chalcogenide Layers. Ag <sub>2</sub> Se Is Excluded Due to Variation               |

| of Write Resistance Values from Changes in Temperature74                                             |

| Table 4.8: Average Second Write Resistance Values from All Temperature Ranges for                    |

| the Varying Chalcogenide Memory Layers75                                                             |

| Table 5.1: Typical Values for GeTe/SnSe/Ag Device Programmed with: 100 nA, 1 µA,                     |

| 10 $\mu$ A, 100 $\mu$ A, and 1 mA Compliance Currents. (-) No Measurable Threshold                   |

| Voltage                                                                                              |

| Table 5.2: Typical Values for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Device Programmed with a 1 mA |

| Compliance Current. (-) Symbolizes No Switch in Resistance at Threshold 97                           |

# LIST OF FIGURES

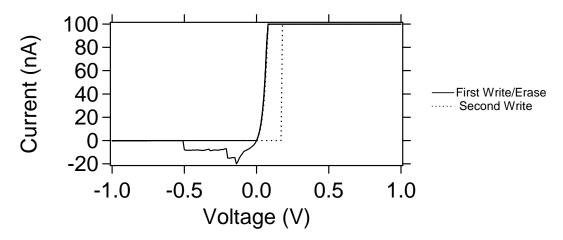

| Figure 1.1: IV Curve for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag device                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1: Cartoon of the Two-Terminal Device Showing the Sandwiched Layers                                                                                                                                                                                                                                                                                                                                                                                           |

| Between Two Tungsten Electrodes. Layer Thicknesses are Not Drawn to                                                                                                                                                                                                                                                                                                                                                                                                    |

| Scale. M Represents: Pb, Sb, Ag, Sn and In9                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2.2: Top Down SEM Image of a Two-terminal Device Showing Top and Bottom                                                                                                                                                                                                                                                                                                                                                                                         |

| Electrodes a) Low Magnification and b) High Magnification Image of Device                                                                                                                                                                                                                                                                                                                                                                                              |

| Contact. Images are Courtesy of Micron Technology                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 2.3: Cross-sectional Representation of Device Including Ge <sub>2</sub> Se <sub>3</sub> Adhesion Layer                                                                                                                                                                                                                                                                                                                                                          |

| Films                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

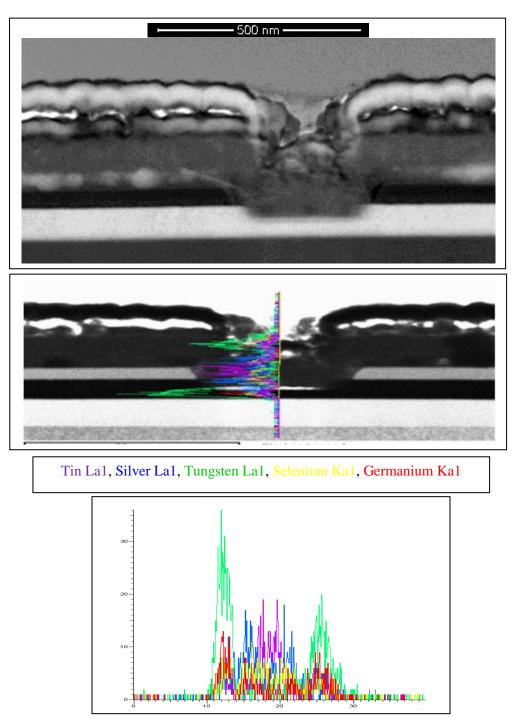

| Figure 2.4: SEM and STEM Elemental Mapping of Contact Between the Top and Bottom                                                                                                                                                                                                                                                                                                                                                                                       |

| Electrodes of a Virgin Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Device. Data Collected at Micron                                                                                                                                                                                                                                                                                                                                                                       |

| Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.5: Example of Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Two-terminal Device Representing a                                                                                                                                                                                                                                                                                                                                                                     |

| Write/Erase/Write Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 3.1: Sample Arrhenius Equation Plot for Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Device Used in                                                                                                                                                                                                                                                                                                                                     |

| Determining Activation Energy                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

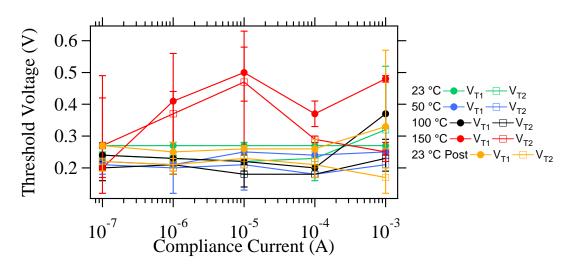

| Figure 3.2: Average Write Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices                                                                                                                                                                                                                                                                                                                                     |

| Figure 3.2: Average Write Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices versus the Programming Compliance Current at Four Different Temperatures.                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| versus the Programming Compliance Current at Four Different Temperatures.                                                                                                                                                                                                                                                                                                                                                                                              |

| versus the Programming Compliance Current at Four Different Temperatures.                                                                                                                                                                                                                                                                                                                                                                                              |

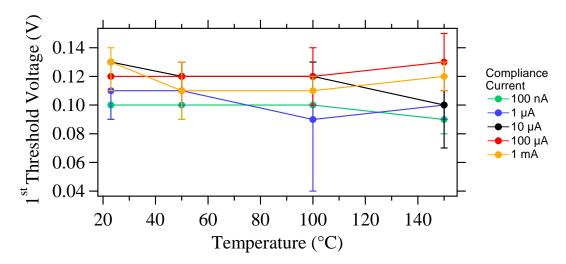

| versus the Programming Compliance Current at Four Different Temperatures.<br>22<br>Figure 3.3: First Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices versus                                                                                                                                                                                                                                                   |

| versus the Programming Compliance Current at Four Different Temperatures.<br>22<br>Figure 3.3: First Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Sb <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices versus<br>Temperature for Five Different Programming Compliance Currents                                                                                                                                                                                 |

| <ul> <li>versus the Programming Compliance Current at Four Different Temperatures.</li> <li>22</li> <li>Figure 3.3: First Threshold Voltages of Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Stack Devices versus</li> <li>Temperature for Five Different Programming Compliance Currents.</li> <li>23</li> <li>Figure 3.4: Second Threshold Voltages for Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Stack Devices versus</li> </ul> |

| Figure 3.6: Example of Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Device Programmed with 100 nA Compliance                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Current at 23 °C                                                                                                                           |

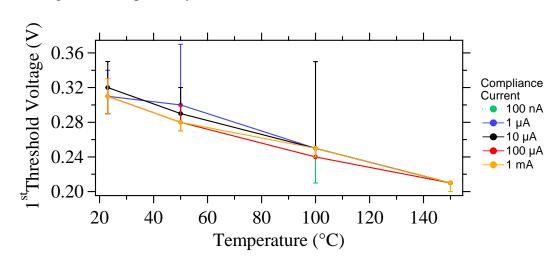

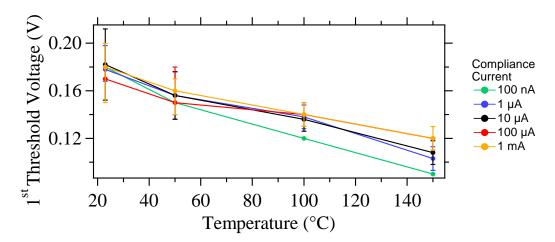

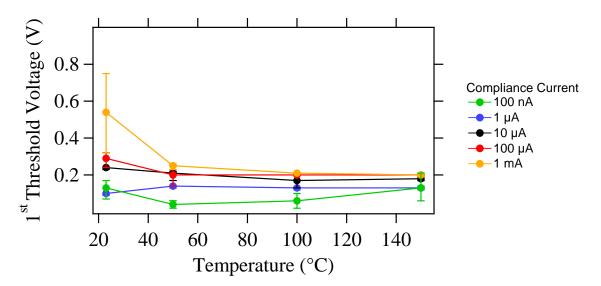

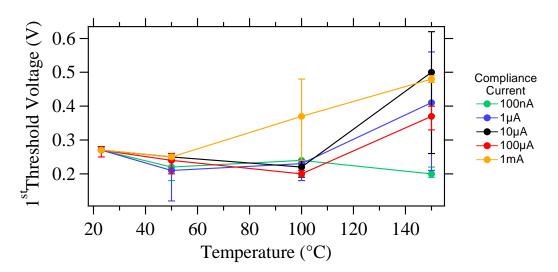

| Figure 3.7: First Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack Devices versus                                      |

| Temperature for Five Different Programming Compliance Currents                                                                             |

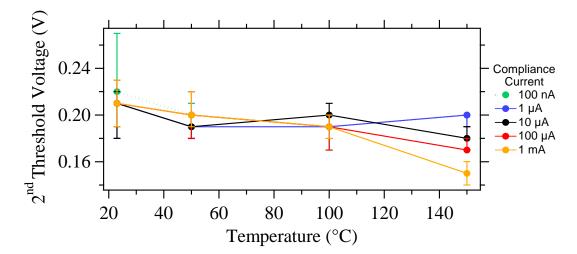

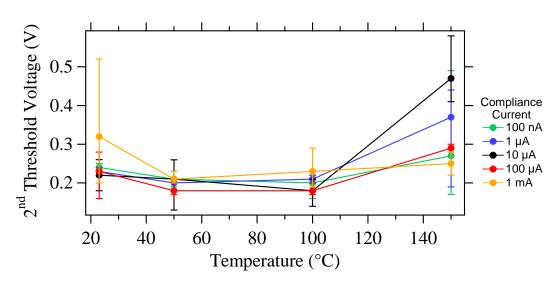

| Figure 3.8: Second Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack Devices versus                                     |

| Temperature for Five Different Programming Compliance Currents                                                                             |

| Figure 3.9: Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Stack Devices versus Compliance                                 |

| Current at Four Different Temperatures                                                                                                     |

| Figure 3.10: Representative IV Write Sweeps of Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Virgin Devices                                     |

| Programmed at 100 nA Compliance Current at Four Different Temperatures.                                                                    |

|                                                                                                                                            |

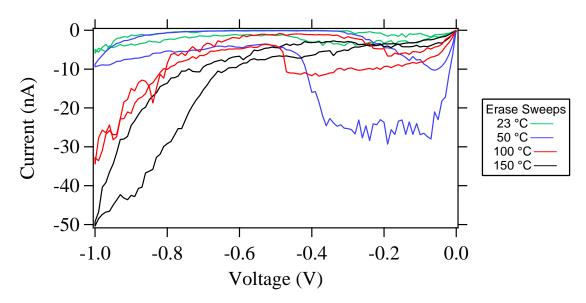

| Figure 3.11: Representative IV Erase Sweeps of Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Virgin Devices                                     |

| Programmed at 100 nA Compliance Current at Four Different Temperatures.                                                                    |

|                                                                                                                                            |

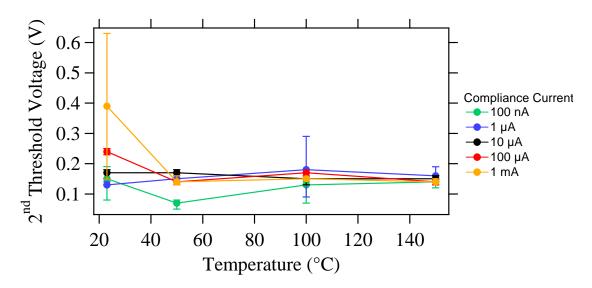

| Figure 3.12: First threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Stack Devices versus                                     |

| Temperature for Five Different Programming Compliance Currents                                                                             |

| Figure 3.13: Second Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Stack Devices versus                                    |

| Temperature for Five Different Programming Compliance Currents                                                                             |

| Figure 3.14: Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag Stack Devices versus Temperature                 |

| for Five Different Compliance Currents                                                                                                     |

| Figure 3.15: First Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag Stack Devices versus                       |

| Temperature for Five Different Compliance Currents                                                                                         |

| Figure 3.16: Second Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag Stack Devices versus                      |

| Temperature for Five Different Compliance Currents                                                                                         |

| Figure 3.17: Threshold Voltages of $Ge_2Se_3/In_2Se_3/Ag$ Stack Devices versus Temperature                                                 |

| for Five Different Compliance Currents                                                                                                     |

| Figure 3.18: Average First Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /In <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices versus |

| Temperature for Five Different Compliance Currents                                                                                         |

| Figure 3.19: Average Threshold Voltages of Ge <sub>2</sub> Se <sub>3</sub> /In <sub>2</sub> Se <sub>3</sub> /Ag Stack Devices versus       |

| Temperature for Five Different Compliance Currents                                                                                         |

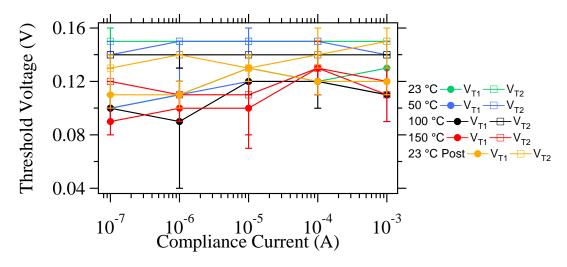

| Figure 3.20: Threshold Voltages of GeTe/SnSe/Ag Stack Devices versus Temperature for                                       |

|----------------------------------------------------------------------------------------------------------------------------|

| Five Different Compliance Currents                                                                                         |

| Figure 3.21: First Threshold Voltages of GeTe/SnSe/Ag Stack Devices versus                                                 |

| Temperature for Five Different Compliance Currents                                                                         |

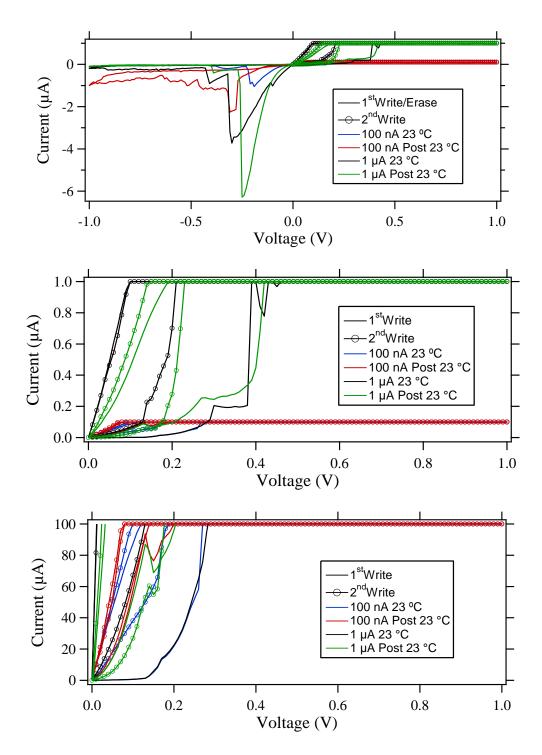

| Figure 3.22: Representative IV Curves of GeTe/SnSe/Ag Stack Devices Programmed at                                          |

| 100nA and 1 $\mu$ A: Top – Full Scale; Middle – Zoomed in 1 $\mu$ A; Bottom –                                              |

| Zoomed in 100 nA                                                                                                           |

| Figure 3.23: Second Threshold Voltages of GeTe/SnSe/Ag Stack Devices versus 44                                             |

| Figure 3.24: IVof Virgin GeTe/SnSe/Ag Stack Device at 150 °C with 1 mA Compliance                                          |

| Current                                                                                                                    |

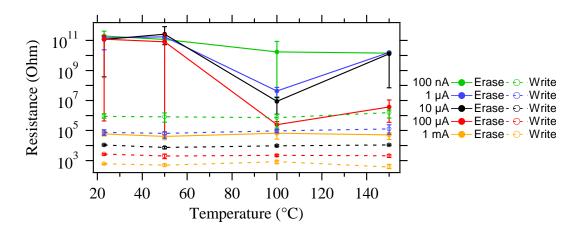

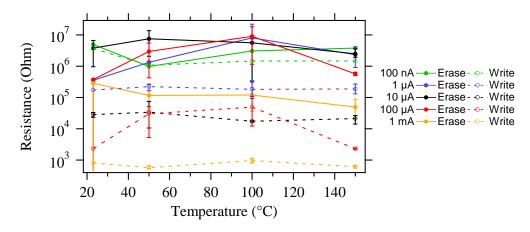

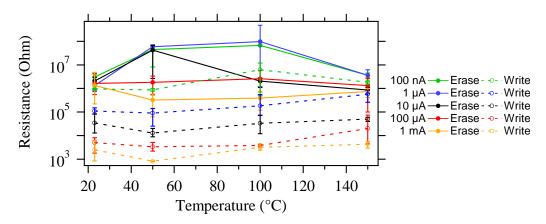

| Figure 4.1: Plot of Erase and Second Write Resistances Versus Temperature with                                             |

| Varying Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / Sb <sub>2</sub> Se <sub>3</sub> /Ag Devices. |

|                                                                                                                            |

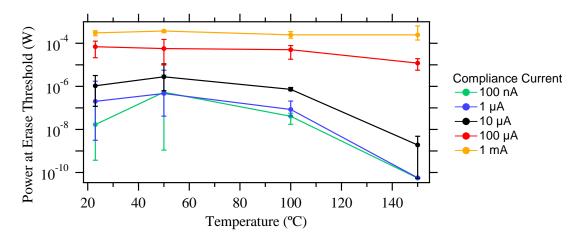

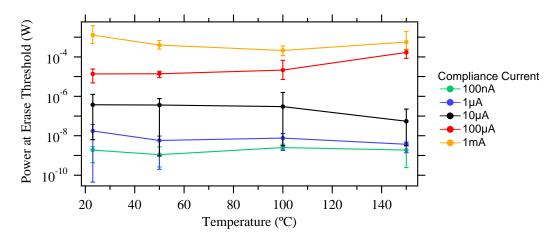

| Figure 4.2: Plot of Power at the Erase Threshold Versus Temperature with Varying                                           |

| Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / Sb <sub>2</sub> Se <sub>3</sub> /Ag Devices          |

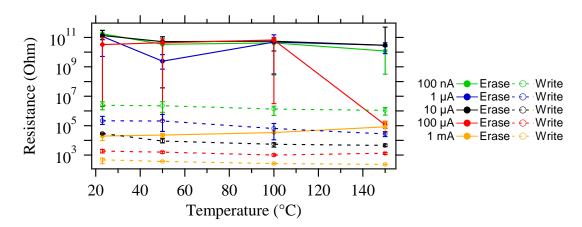

| Figure 4.3: Plot of Erase and Second Write Resistances Versus Temperature at Five                                          |

| Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/ Ag Stack                                        |

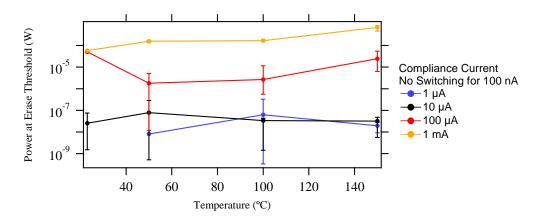

| Figure 4.4: Plot of Power at Erase Threshold at Four Temperatures for Five Programming                                     |

| Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / SnSe/Ag Devices                                                  |

| Figure 4.5: Plot of Erase and Second Write Resistances Versus Temperature for Five                                         |

| Programming Currents for Ge <sub>2</sub> Se <sub>3</sub> /PbSe/Ag Stack61                                                  |

| Figure 4.6: Plot of Power at Erase Threshold Versus Temperature with Varying                                               |

| Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / PbSe/Ag Devices                                      |

| Figure 4.7: Plot of Erase and Second Write Resistances Versus Four Temperatures for                                        |

| Five Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> /Ag <sub>2</sub> Se/Ag Stack64                    |

| Figure 4.8: Plot of Power at Erase Threshold Versus Temperature with Five                                                  |

| Programming Currents for Ge <sub>2</sub> Se <sub>3</sub> / Ag <sub>2</sub> Se/Ag Devices                                   |

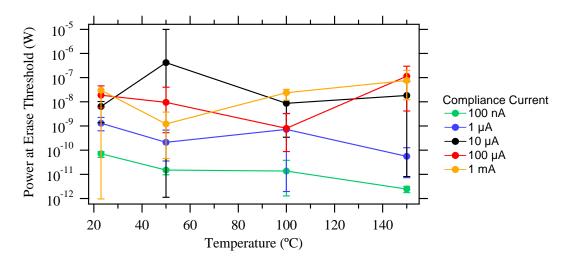

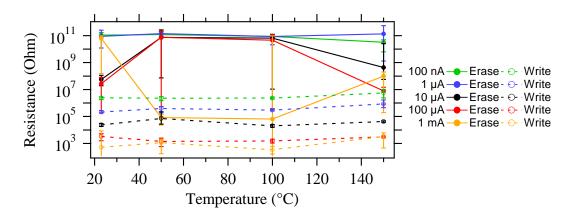

| Figure 4.9: Plot of Erase and Second Write Resistances Versus Temperature at Varying                                       |

| Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / In <sub>2</sub> Se <sub>3</sub> / Ag Stack           |

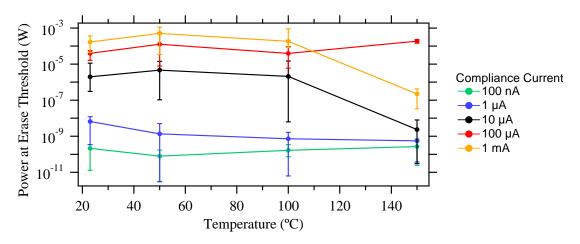

| Figure 4.10: Plot of Power at Erase Threshold Versus Temperature with Five                                                 |

| Programming Compliance Currents for Ge <sub>2</sub> Se <sub>3</sub> / In <sub>2</sub> Se <sub>3</sub> /Ag Devices          |

|                                                                                                                            |

| Figure 4.11: Plot of Erase and Second Write Resistances Versus Temperature for Five                                             |

|---------------------------------------------------------------------------------------------------------------------------------|

| Programming Currents for GeTe/SnSe/Ag Stack70                                                                                   |

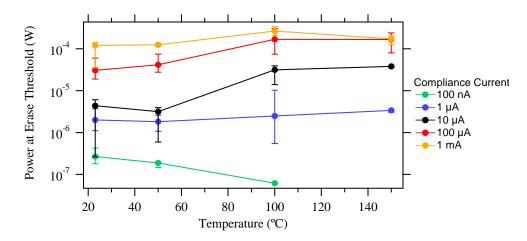

| Figure 4.12: Plot of Power at Erase Threshold Versus Temperature with Varying                                                   |

| Programming Compliance Currents for GeTe/ SnSe/Ag Devices72                                                                     |

| Figure 5.1: Image of an Aracor 4100 Wafer-Level X-ray Irradiator (17)                                                           |

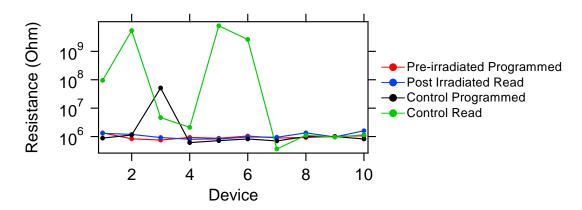

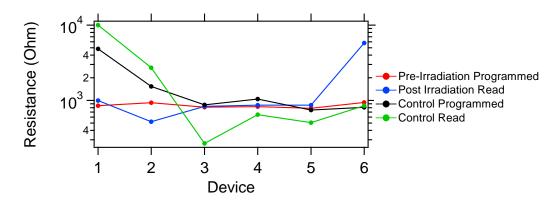

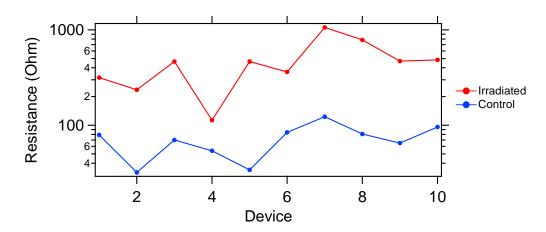

| Figure 5.2: Plot of Resistances for GeTe/SnSe/Ag Stack Irradiated and Control Devices                                           |

| with a Programming 100 nA Compliance Current                                                                                    |

| Figure 5.3: Plot of Resistances for GeTe/SnSe/Ag Stack Irradiated and Control Devices                                           |

| with a Programming 100 µA Compliance Current                                                                                    |

| Figure 5.4: Plot of Resistances for GeTe/SnSe/Ag Stack Irradiated and Control Devices                                           |

| with a Programming 1 mA Compliance Current.                                                                                     |

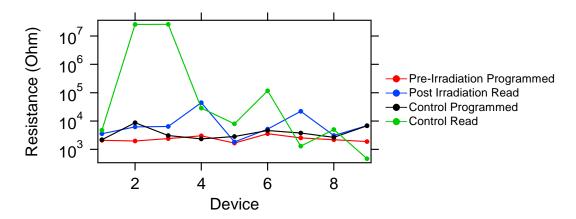

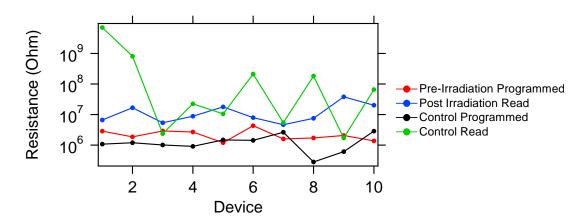

| Figure 5.5: Plot of Resistances for Irradiated Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack and Control Devices               |

| with a Programming 100 nA Compliance Current                                                                                    |

| Figure 5.6: Plot of Resistances for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack Irradiated and Control Devices               |

| with a Programming 100 µA Compliance Current                                                                                    |

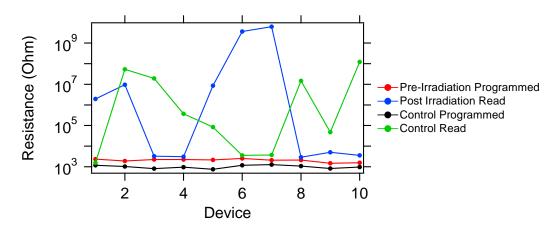

| Figure 5.7: Plot of Resistances for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack Irradiated and Control Devices               |

| with a Programming 1 mA Compliance Current                                                                                      |

| Figure 5.8: Plot of Difference in Programmed Resistance and Read Resistances for                                                |

| Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Stack Irradiated and Control Devices with a Programming 1                              |

| mA Compliance Current                                                                                                           |

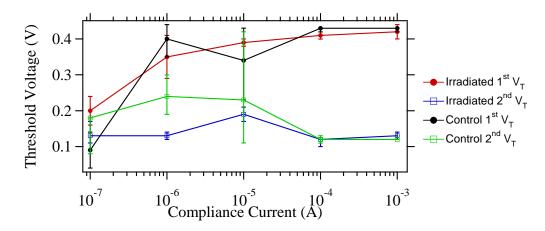

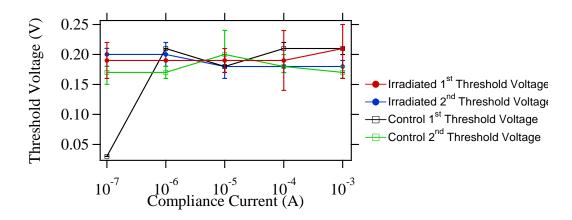

| Figure 5.9: 1 <sup>st</sup> and 2 <sup>nd</sup> Threshold Voltages for Irradiated and Control GeTe/SnSe/Ag                      |

| Devices                                                                                                                         |

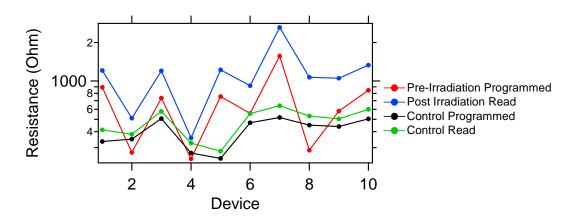

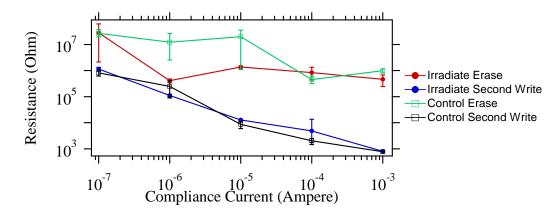

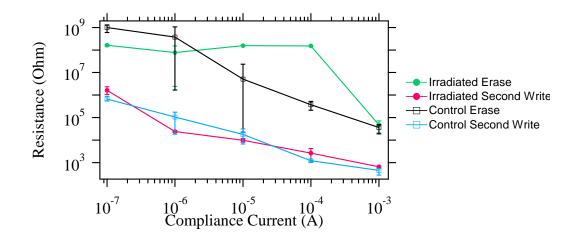

| Figure 5.10: Write and Erase Resistances for Irradiated and Control GeTe/SnSe/Ag                                                |

| Devices                                                                                                                         |

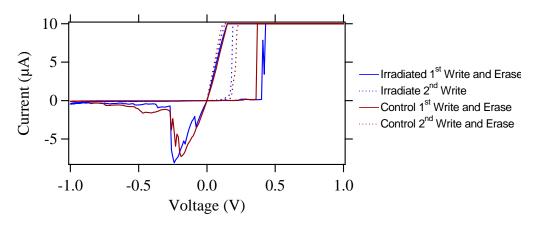

| Figure 5.11: Representative DC Sweep Traces of Control and Irradiated GeTe/SnSe/Ag                                              |

| Devices while Programming with 10 µA Compliance Current                                                                         |

| Figure 5.12: 1 <sup>st</sup> and 2 <sup>nd</sup> Threshold Voltages for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Devices During |

| Irradiation and Non-Irradiated Controls                                                                                         |

| Figure 5.13: Write and Erase Resistances for Ge <sub>2</sub> Se <sub>3</sub> /SnSe/Ag Devices During Irradiation                |

| and Non-Irradiated Controls                                                                                                     |

#### **CHAPTER 1: INTRODUCTION**

#### **1.1 Introduction and Motivation**

There is an assemblage of personal media devices that use non-volatile electronic memory (NVM) that are increasingly in demand, such as digital cameras, music players, and cell phones. NVM is distinguished from volatile memory (such as Dynamic Random Access Memory) in that it retains its data state in the absence of power to the memory.

The leading NVM device is Flash. A Flash device uses a charge storage mechanism that requires a high voltage, 5 to 8 V or more, to operate. Flash has a few disadvantages for many applications, however. First, it is damaged by radiation. Flash memory can, thus, lose its data state or be rendered nonfunctional if exposed to radiation. Second, the high voltage requirements of Flash make it unattractive in applications for which low power operation is necessary. Third, because of the way Flash stores the data state, a scaling limit is close to being reached, which will prevent higher density memory arrays from being realized. For these reasons, new types of NVM are under investigation in the hopes that Flash can be replaced with a memory device that is not prone to any of the disadvantages of Flash.

The ideal NVM should be low cost, have fast write and read access times, low energy consumption, high cycling endurance greater than  $10^7$  cycles (1), and reliable data retention in standard conditions and conditions of radiation exposure. Devices that are

currently being explored include resistive variable devices, such as phase change memory, resistive oxide memory, and ion-conducting memory devices.

In this work, ion-conducting devices using layers of chalcogenide materials are explored as potential non-volatile memory devices. This technology is also known in the literature as conductively bridged RAM (CBRAM), programmable metallization cell (PMC), and programmable conductor RAM (PCRAM; not to be confused with the acronym PCRAM as used to denote phase change memory).

#### 1.2 Overview of Ion-Conducting Variable Resistance Devices

Ion-conducting devices are composed of a medium that is amorphous and that acts as an insulator and a metal ion storage medium, as well as a source of metal ions. The source of metal ions is an electrochemically active material that is enclosed next to the amorphous medium between two electrode pads, forming a simple metal-insulatormetal (MIM) structure. The most common electrochemically active metals used are Ag or Cu. Common amorphous materials used include oxides and chalcogenides.

The devices are commonly fabricated in a high resistance state. When a voltage bias is applied to the anode, the active metal will oxidize and become a positive ion. The positively charged metal ion will drift due to the induced electric field through the amorphous layer. When the positively charged metal ion reaches the cathode, it will be reduced and become neutral; this process is referred to as electro-deposition. Additional positively charged metal ions will then reach the now neutral metal and be reduced. This sequence continues until the active metal creates a conductive channel between the two electrodes. The conductive channel will be thicker in shape at the cathode because the bulk of electro-deposition occurs there (2). When a bias voltage of opposite polarity is applied, the cathode becomes the anode and vice versa. The neutral metal in the conductive channel will be oxidized once again and drift with the electric field, which is in the opposite direction from before. Because of the lack of an active metal source on the cathode side of the device, the conductive channel will be severed, and the device will be in a high resistance state. These devices exhibit bipolar switching, meaning that reversed voltage polarities are required to change the state of the devices. The ion-conducting devices are read by applying a potential across the device and measuring the resistance. The state of the ion-conducting device is defined by the resistance value.

The research in this thesis investigates the effects on device operating parameters of Ag in various chalcogenide glasses as the medium with an additional metal-selenide layer.

#### 1.2.1 Operation of Silver Ion Migration Through Chalcogenide Glasses

The exact mechanism by which the Ag (or Cu) forms and dissolves as a conductive channel is not fully understood. One theory is that the amorphous chalcogenide films provide pathways for fast transport of cations like silver in a reduction-oxidation (redox) reaction when a potential is applied to the electrodes (3; 4). This theory assumes that the silver is electroplated on the bottom electrode when reduced from a cation to a neutral atom and that the silver cations continue to electro-deposit until they reach the top electrode. The ease with which this happens not only depends on the applied potential but also on the structure of the amorphous chalcogenide. Another theory is that Ag will form a bond with Se, which provides a shorter pathway for the silver cations to drift in an electric field before being reduced (1; 5). Recently, a model using density functional theory of Ag in Ge<sub>2</sub>Se<sub>3</sub> has hypothesizes that Ag will displace the germanium (Ge) from Ge-Ge bonds to form strong Ag-Ge bonds, also creating shorter pathways for subsequent reformations of a silver conductive pathway (6).

The ion-conducting two-terminal devices fabricated in this study consist of layers from top to bottom: tungsten top electrode, silver layer, metal-selenide layer, germaniumchalcogenide layer, and a tungsten bottom electrode. The varying metal in the metalselenide layer are lead (Pb), antimony (Sb), tin (Sn), indium (In), or silver (Ag). The chalcogenide in the germanium-chalcogenide layer is either selenium (Se) or tellurium (Te). In addition to those layers, there are adhesion Ge<sub>2</sub>Se<sub>3</sub> layers that are described further in Chapter 2. The device is considered 'ON' when in a low resistance state and 'OFF' when in a high resistance state. The ion-conducting device will be in a high resistance state when fabricated due to the chalcogenide amorphous layers behaving as an insulator between two metal electrodes. The silver is easily oxidized and releases an electron to the adjoining chalcogenide layer or to the anode (top electrode) when a very small potential is applied in order to form the ion Ag<sup>+</sup>. To write to a low resistance state, the device requires a positive voltage bias sweep to the top electrode, which produces an electric field in which the Ag<sup>+</sup> ions drift through the chalcogenide layers and reduce at the bottom electrode. When the silver eventually spans the top and bottom electrodes,

forming a conductive channel, the device will be in a low resistance state. A negative potential applied to the top electrode will sever the silver conductive channel, and the device will be in a high resistance state again.

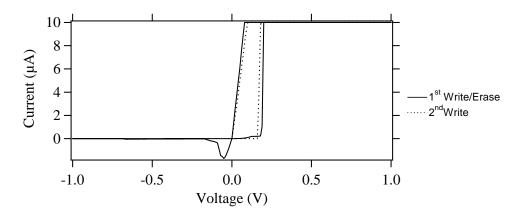

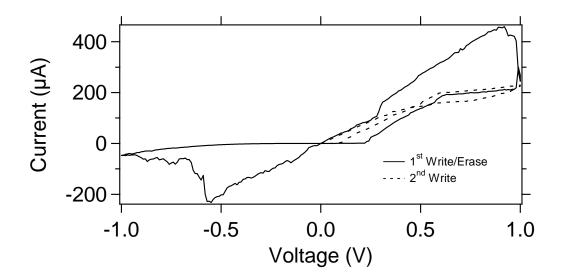

A voltage versus current (IV) curve from a DC sweep of an ion-conducting device shows a distinct 'ON' and 'OFF' resistance state. An example IV curve for an ionconducting device is shown in Figure 1.1. The two-terminal device in the figure had a positive double DC sweep from 0 V to 1 V and back to 0 V applied to the top electrode. Then, a subsequent negative double DC sweep from 0 V to -1 V and back to 0 V was administered to the top electrode. The two separate measurements are combined into one graph in Figure 1.1. The positive DC sweep had a compliance current of 10  $\mu$ A in order to prevent excess current through the device when it switched rapidly to a low resistance state.

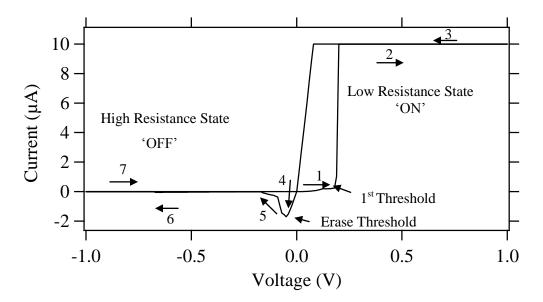

Figure 0.1: IV Curve for Ge<sub>2</sub>Se<sub>3</sub>/SnSe/Ag device.

The DC sweep of Figure 1.1 is somewhat misleading because it looks as if the voltage increases to 1V; that, however, is not the case. When the sweep reaches the critical voltage labeled as the 1<sup>st</sup> threshold in Figure 1.1 and referred in this study as  $V_{T1}$ , the current increases to the compliance current set by the parameter analyzer. The positive DC sweep measurement still continues through the number of steps set up in the procedure, but the actual applied potential clamps at the voltage at which the compliance current is maintained, which is less than the threshold voltage. This effect is seen in the number 3 trace in Figure 1.1, which has a lower voltage than the  $V_{T1}$  when it returns to 0 V. The positive DC sweep is considered the Write Sweep because you are 'writing' or programming the device into a low resistance.

At the erase threshold, the device goes from a low resistance state to higher resistance state when the conductive silver channel has been disrupted during the application of a negative potential. This negative DC sweep is considered the Erase Sweep because you have 'erased' the device's programmed low resistance and returned it to a high resistance state. The erase sweep is asymmetric to the write sweep as evident in Figure 1.1 and has 1 mA compliance current to restrict current flow. Commonly, the resistance at the erase threshold is not the highest resistance of the device; there is still some conductivity as seen in the number 5 trace in Figure 1.1.

The threshold voltage of an ion-conducting device will be dependent on the ease of the ion movement through the medium with an applied electric field. Within the same material system, the greater the film thickness results in a greater threshold voltage. It has been modeled that within the  $Ge_2Se_3$  system, Ag readily releases an electron to become Ag<sup>+</sup> (6). With an increased distance for the Ag<sup>+</sup> ion to drift, a larger potential is needed to create the adequate electric field.

The ion-conducting device can be programmed into variable resistance states during the write sweep by limiting the amount of current allowed through the device. The 'ON' resistance is inversely proportional to the magnitude of the compliance current; e.g., a higher compliance current will create a lower 'ON' resistance.

The 'ON' state is dependent on the silver conductive channel, which is assumed to be much smaller than the device area and hence independent of electrode size contact (7). The high resistance 'OFF' state can be increased by reducing the contact electrode area (8). This effect is explained by the classic equation for resistance,  $R = \rho \frac{l}{A}$ . Where  $\rho$  is the electrical resistivity of the material, *l* is the length or thickness, and *A* is the crosssectional area.

### **1.3 Summary of Thesis**

To achieve the role as a universal memory, there are certain guideline values that need to be achieved. The NVM should achieve a high ('OFF') and low ('ON') resistance value difference greater than an order of magnitude with data retention of greater than ten years, and it should utilize write/erase voltages of a few hundred mV and pulse times less than 10  $\mu$ s to compete with Flash. Ion-conducting devices are a contender in the race for a universal memory.

The characteristics of ion-conducting devices can be modified by the choice of chalcogenide glass and metal-chalcogenide material. In this research, the electrical switching characteristics of devices comprised of metal chalcogenide layers consisting of various metal-selenides (with the metal either being Pb, Sn, Sb, Ag, or In) and a Ge<sub>2</sub>Se<sub>3</sub>-chalcogenide layer are compared. Additionally, a comparison of the SnSe:Ge<sub>2</sub>Se<sub>3</sub>-based device and the SnSe:GeTe-based device is performed.

Chapter 2 provides a description of the devices studied and the electrical tests performed in this work. Chapters 3 and 4 present electrical measurement results for the devices under study and discuss trends in electrical switching properties with respect to the metal chalcogenide layer and the chalcogenide glass layer. Chapter 5 presents electrical characterization results during and after total ionizing dose radiation testing. Lastly, Chapter 6 provides of summary of the key results of this research.

# CHAPTER 2: ION-CONDUCTING DEVICES: MATERIALS AND ELECTRICAL CHARACTERIZATION METHODOLOGY

### **2.1 Introduction**

In this chapter, the description of the germanium-chalcogenide/metal-selenide/Ag ion-conducting device layout, fabrication, materials, and electrical characterization measurements are discussed.

## 2.2 Ion-Conducting Two-Terminal Device Layout

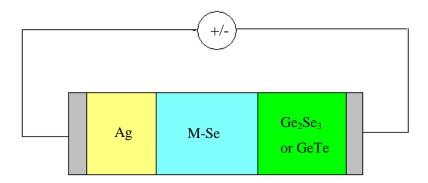

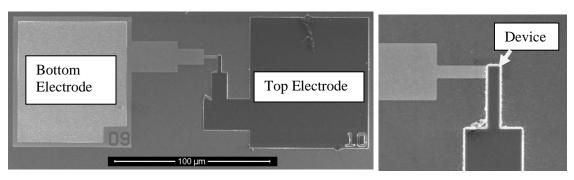

All devices tested in this work had the same two-terminal device layout consisting of tungsten electrodes with varying stacked layers in a 0.25  $\mu$ m contact. A pictorial representation of the device is shown in Figure 2.1. A SEM top-down image of a fabricated two-terminal device used in this work is shown in Figure 2.2.

Figure 2.1: Cartoon of the Two-Terminal Device Showing the Sandwiched Layers Between Two Tungsten Electrodes. Layer Thicknesses Are Not Drawn to Scale. M Represents: Pb, Sb, Ag, Sn, and In

Figure 2.2: Top-Down SEM Image of a Two-Terminal Device Showing Top and Bottom Electrodes a) Low Magnification and b) High Magnification Image of Device Contact. Images Are Courtesy of Micron Technology.

Figure 2.2 is a top-down SEM image of an untested two-terminal device. The two terminals are labeled as bottom electrode and top electrode. The large electrodes are needed for proper probe tip placement to perform electrical testing. The magnified image of the two metal lines from the electrodes intersection points out the location of the 0.25 µm contact where the device actually resides. The metal lines provide the path from the electrodes to the device. Note the residue on the top electrode. The residue is unremoved photoresist. The unaltered photoresist on the top electrode acts as an indicator for untested (virgin) devices. The probe tip will leave a scratch in the photoresist when performing electrical testing on the devices and provides a marker that the device has been previously tested.

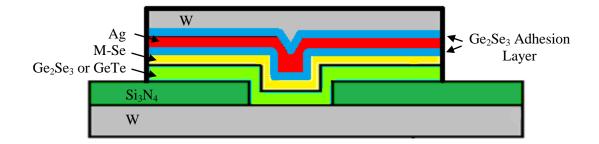

A cross-section of the device's film layers as deposited is shown in Figure 2.3. The layer thicknesses are not drawn to scale and act as a reference. The target film thicknesses are provided in Table 2.1. The  $Ge_2Se_3$  adhesion layers (shown in Figure 2.3) are not listed in Table 2.1 since they are not key layers for device operation but are necessary only for electrode adhesion. In all devices, the adhesion layers include 150 Å and 100 Å  $Ge_2Se_3$  between the M-Se/Ag films and Ag/W films, respectively.

Figure 2.3: Cross-Sectional Representation of Device Including Ge<sub>2</sub>Se<sub>3</sub> Adhesion Layer Films.

| Device | Bottom    | Germanium-                      | Metal-                          | Ag    | Top       |

|--------|-----------|---------------------------------|---------------------------------|-------|-----------|

| #      | Electrode | Chalcogenide                    | Selenide                        |       | Electrode |

| 1      | W         | Ge <sub>2</sub> Se <sub>3</sub> | Sb <sub>2</sub> Se <sub>3</sub> | Ag    | W         |

|        | 350Å      | 300 Å                           | 500 Å                           | 500 Å | 350 Å     |

| 2      | W         | Ge <sub>2</sub> Se <sub>3</sub> | SnSe                            | Ag    | W         |

|        | 350 Å     | 300 Å                           | 500 Å                           | 500 Å | 350 Å     |

| 3      | W         | Ge <sub>2</sub> Se <sub>3</sub> | PbSe                            | Ag    | W         |

|        | 350 Å     | 300 Å                           | 1000 Å                          | 500 Å | 350 Å     |

| 4      | W         | Ge <sub>2</sub> Se <sub>3</sub> | Ag <sub>2</sub> Se              | Ag    | W         |

|        | 350 Å     | 300 Å                           | 500 Å                           | 500 Å | 350 Å     |

| 5      | W         | Ge <sub>2</sub> Se <sub>3</sub> | In <sub>2</sub> Se <sub>3</sub> | Ag    | W         |

|        | 350 Å     | 300 Å                           | 500 Å                           | 500 Å | 350 Å     |

| 6      | W         | GeTe                            | SnSe                            | Ag    | W         |

|        | 350 Å     | 300 Å                           | 500 Å                           | 500 Å | 350 Å     |

Table 2.1: Table of the Devices Tested in This Work and Corresponding Target

Film Thicknesses.

A cross-sectional SEM image of a device of type 2 with Ge<sub>2</sub>Se<sub>3</sub>/SnSe (see Table 2.1) is shown in Figure 2.4. The corresponding STEM mapping of the device is also provided.

Figure 2.4: SEM and STEM Elemental Mapping of Contact Between the Top and Bottom Electrodes of a Virgin Ge<sub>2</sub>Se<sub>3</sub>/SnSe/Ag Device. Data Collected at Micron Technology.

The STEM mapping demonstrates the difficulty of using SEM and STEM techniques to investigate structure of ion-conducting devices that use Ag. In all cases, Ag moves easily under the influence of an electron beam. Samples are always compromised during sample prep, as the Ag will move between layers during preparation of a sample with a focused ion beam as well as during imaging. Figure 2.4 shows clearly that silver has migrated throughout the chalcogenide device during imaging in an untested device.

### 2.3 Fabrication of Ion-Conducting Two-Terminal Devices

The two-terminal devices were fabricated on 200 mm p-type Si wafers. The bottom and top W electrodes and Ag were deposited by sputtering. The bottom electrode received an argon sputter etch prior to chalcogenide deposition to remove any native oxide growth. The Ge<sub>2</sub>Se<sub>3</sub> layers were deposited by sputtering with an Ulvac ZX-1000 RF sputtering tool. The remaining materials were purchased from Alfa Aesar with 99.999% purity: GeTe, SnSe, PbSe, Sb<sub>2</sub>Se<sub>3</sub>, Ag<sub>2</sub>Se, and In<sub>2</sub>Se<sub>3</sub>. These materials were all thermally evaporated using a CHA Industries SE-600-RAP thermal evaporator with a base system pressure of 1 x 10<sup>-7</sup> torr. A summary of film compounds and target thicknesses are shown in Table 2.1.

### 2.4 Chalcogenide Film Choices

Chalcogenide refers to the elements and the materials containing those elements in column six of the periodic table: sulfur (S), selenium (Se), and tellurium (Te). In 1968, Ovshinsky discovered the phase-change resistive switching in the chalcogenide film  $Te_{48}As_{30}Si_{12}Ge_{10}$  (9). The switching resistance states of chalcogenide compounds discovery led to phase-change memory and the compact disk (CD) technology. In 1976, Hirose and Hirose found a reversible resistance switching effect in Ag-photodoped  $As_2S_3$ films (10). This discovery was the catalyst for the later work on ion-conducting resistance-variable devices and ultimately on the device studies in this work.

#### 2.4.1 Metal-Selenide Layer Choices

The metals used for the metal selenide layer were Sb, Sn, Pb, Ag, and In. These metal-selenide materials are readily commercially available and can be thermally evaporated. Under study in this work is an investigation of the involvement, if any, of the metal-ion species in the metal-selenide layer, including whether the metal-ion species affects the formation of a conducting pathway through the chalcogenide glass layer. Any effects would be realized in variations of threshold voltages, resistances, and power requirements for switching between high and low resistance states. Possible methods by which the metal-ion could influence the device's electrical properties include the metal ion assisting in formation of the conductive channel during the first write operation, the metal-ion participating in a redox reaction with the Ag, the metal-ion species drifting with  $Ag^+$  in the electric field, or the steric effects of the metal-selenide species hindering the motion of  $Ag^+$  through the layer.

The theory of a redox reaction involves the transfer of electrons between two different atoms or molecules. A species is reduced when it gains an electron and acts as an oxidizing agent. A species is oxidized when it loses an electron and acts as a reducing agent. A reduction potential is a value that gives the tendency of a species to be reduced. A species with a higher (more positive) reduction potential will have a tendency to gain an electron from a species with a lower reduction potential. Table 2.2 lists the standard reduction potentials of the metals used in an aqueous environment at 25 °C, excluding the metal Sb (11). The chosen reduction reaction for Sb in an acidic environment at 25 °C is used due to the lack of a reduction potential of Sb<sup>3+</sup> in an aqueous environment.

| Metal            | Cathode (Reduction)                                                      | Half Reaction<br>Standard Potential E <sup>0</sup><br>(V) |

|------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|

| Ag               | $Ag^{+} + e^{-} \leftrightarrow Ag(s)$                                   | +0.799                                                    |

| Sb               | $Sb_2O_3(s) + 6H^+ + 6e^- \leftrightarrow 2Sb(s) + 3H_2O$                | +0.147                                                    |

| Sn <sup>4+</sup> | $\operatorname{Sn}^{4+} + 2e^{-} \leftrightarrow \operatorname{Sn}^{2+}$ | +0.139                                                    |

| Pb               | $Pb^{2+} + 2e^{-} \leftrightarrow Pb(s)$                                 | -0.126                                                    |

| Sn <sup>2+</sup> | $\operatorname{Sn}^{2+} + 2e^{-} \leftrightarrow \operatorname{Sn}(s)$   | -0.141                                                    |

| In               | $In^{3+} + 3e^{-} \leftrightarrow In(s)$                                 | -0.338                                                    |

Table 2.2: Table of Standard Reduction Potentials of Metals from Metal-Selenide Layer (11).

Table 2.2 lists the metals with decreasing reduction potentials from top to bottom. Since silver has the most positive reduction potential from all of the other metals, silver at the interface of the two layers will be reduced by each of the metals from the metal-selenide layer without an applied voltage bias.

The metal ions have the possibility of also drifting with the electric field, just as  $Ag^+$  does, and of being reduced at the bottom electrode. It has been shown that Sn from

SnSe migrates into  $Ge_2Se_3$  and GeTe layers with an applied potential bias (12; 13). The oxidized metals could perhaps assist in the formation of the conductive channel.

#### 2.4.2 Germanium-Chalcogenide Layer Choices

The two varying germanium chalcogenides used are GeTe and Ge<sub>2</sub>Se<sub>3</sub>. The Ge<sub>2</sub>Se<sub>3</sub> film was sputtered with a physical vapor deposition target composed of pressed Ge<sub>2</sub>Se<sub>3</sub> powder and film is amorphous as deposited. The GeTe was thermally evaporated and is amorphous as deposited. An air break was performed between the GeTe deposition and the subsequent SnSe thermal evaporation deposition to mimic the Ge<sub>2</sub>Se<sub>3</sub> exposure to air during transportation from the sputter tool to the thermal evaporator. These two compounds are chosen to compare the role of the chalcogenides (Se vs. Te) and their glass structures and properties on the device switching properties. Both compounds contain homopolar Ge-Ge bonds (6; 14). The Ge-Ge bonds are predicted through models by Edwards and Campbell to break and form new bonds with Ag in a Ge<sub>2</sub>Se<sub>3</sub> system (6). Both selenium and tellurium are in the chalcogen family and exhibit similar properties. But they are different in size and that difference influences the electronegativity, bonding, and sterics; and they have different amorphous glass structures and properties. For example, the glass transition temperature of  $Ge_2Se_3$  is greater than 613 K but only 423 K for GeTe thin films (12).

### **2.5 Electrical Testing Description**

DC sweeps using a parameter analyzer to apply a potential across a device and during application of the potential the current through the device was measured. The DC sweeps were performed using an HP 4156A Semiconductor Parameter Analyzer to provide the DC sweep and resultant IV curve. The compliance currents on the measurement were varied to 'set' the maximum device programming current during testing. Electrical contact was made to the devices by using micromanipulators with W Micromanipulator 7B probe tips to contact the top and bottom electrodes.

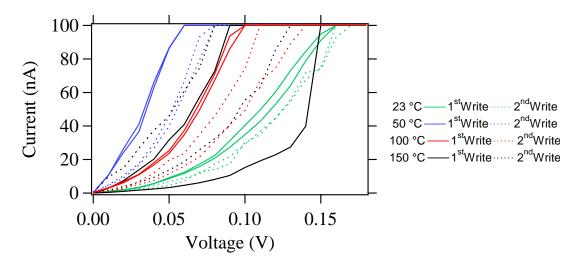

An initial programming DC sweep on a virgin device is performed by first applying a positive double sweep, followed by a negative double sweep, followed by a final positive double sweep. This test sequence is referred to as the write/erase/write (W/E/W) cycle. The positive double sweeps were from 0 V to 1 V and back to 0 V with varying compliance currents of 100 nA, 1  $\mu$ A, 10  $\mu$ A, 100  $\mu$ A, and 1 mA, with the bottom electrode grounded. This test is referred to as the 1<sup>st</sup> write cycle. Immediately following the first positive double sweep, a double sweep from 0 V to -1V and back to 0 V with 1 mA compliance current was performed. The negative sweep is known as the erase cycle. A subsequent positive double sweep with same parameters as the first positive sweep then follows. The second positive DC sweep is referred as the 2<sup>nd</sup> write cycle. Each W/E/W cycle was performed on virgin devices with a minimum of three to five devices per temperature and compliance current. An example I-V plot showing data for an actual W/E/W cycle is shown in Figure 2.5.

Figure 2.5: Example of Ge<sub>2</sub>Se<sub>3</sub>/SnSe/Ag Two-Terminal Device Representing a Write/Erase/Write Cycle.

Temperature studies were performed on a temperature controlled wafer stage with an accuracy of  $\pm 1$  °C on the backside of the wafer; the top of the wafer (the device side) was exposed to ambient. The electrical measurements were taken at temperatures of 23 °C, 50 °C, 100 °C, and 150 °C. The cleaved wafer was placed on the stage, and room temperature (23 °C) measurements were first performed on the two-terminal devices. The wafer remained on the stage while it was heated to the desired temperature, and then the wafer was allowed to equilibrate for a minimum of 15 minutes. After equilibration, the W/E/W cycle was performed on three to five virgin devices for each of the five compliance currents at that temperature. Attempts were made to prevent air cooling on the wafer surface from any air movement in the room.

### **2.6 Conclusion**

In this chapter, the layout and cross-section of the layered chalcogenide twoterminal devices are provided. The choice of materials and fabrication methods were introduced. Lastly, the electrical measurement methodology was provided.

#### **CHAPTER 3: WRITE THRESHOLD VOLTAGE CHARACTERISTICS**

#### **3.1 Introduction**

This chapter discusses the measured threshold voltages of each of the chalcogenide ion-conducting devices listed in Table 2.1, as a function of temperature and programming current (compliance current on the semiconducting parameter analyzer). The electrical measurements performed are described in Chapter 2. The device threshold voltages are compared to determine trends due to the various metal-chalcogenide and germanium-chalcogenide layers. The bars above and below the average values in graphs are high and low, respectively. The erase thresholds are discussed as power requirements to erase in Chapter 4.

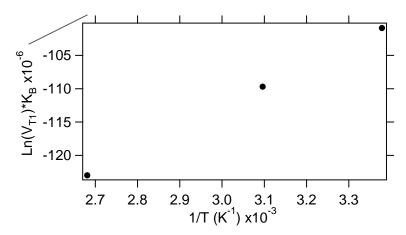

The activation energies are calculated from the Arrhenius equation and by solving for activation energy,  $E_A = -R \frac{\partial V_{T1}}{\partial \frac{1}{T}}$ , where R is Boltzmann's Constant,  $k_B = 8.617 \times 10^{-5}$ eV K<sup>-1</sup>. This approach assumes a first order reaction. The 150 °C V<sub>T1</sub> value is not used in this calculation due to the unusual behavior exhibited with these devices at the elevated temperature (as will be discussed), which is beyond the operating specification requirements for IC devices. An example plot to obtain the activation energy is seen in Figure 3.1.

Figure 3.1: Sample Arrhenius Equation Plot for Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Device Used in Determining Activation Energy.

The Arrhenius equation plot of Figure 3.1 has a y-axis that is  $\ln(V_{T1})*k_B$  and the x-axis is inverse temperature in Kelvin. The slope of this plot will provide the activation energy for the electro-deposition of silver through the medium.

For outlier statistical data points, a q-test was performed to determine if the data

point is random or relevant to the data set. The q

value=  $\frac{difference \ of \ outlier \ and \ nearest \ data \ point}{range \ of \ data \ set}$  is compared to a critical Q table easily viewed on the internet or in literature (15). If q is greater than  $Q_{critical}$ , the suspect measurement can be rejected; otherwise, it is retained. The q-test is often used for fast evaluation of small data sets, commonly three to ten measurements (15).

# 3.2 Compliance Current and Temperature Effects

We begin this section by exploring the compliance current and temperature effects on the threshold voltage of the write sweeps. When the first programming sweep is performed on a virgin device and the device is then erased, the threshold voltage of the second and subsequent writes will differ from the threshold voltage of the first write. This is likely due to the ease at which the  $Ag^+$  ion can migrate along the conduction pathway that was formed during the first write sweep. The DC sweeps used for the measurements discussed in this section were described in Chapter 2. The DC sweeps performed had compliance currents of 100 nA, 1 µA, 10 µA, 100 µA, and 1mA. The temperatures at which testing was administered were 23 °C, 50 °C, 100 °C, and 150 °C and retested at 23 °C post thermal exposure.

## $3.2.1 \underline{Ge_2Se_3/Sb_2Se_3/Ag}$

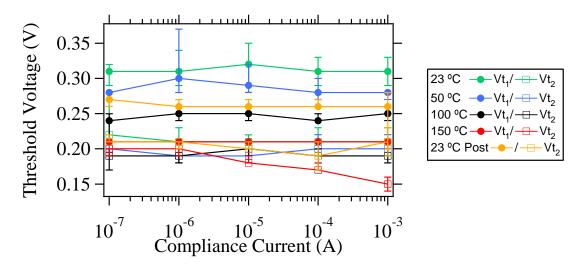

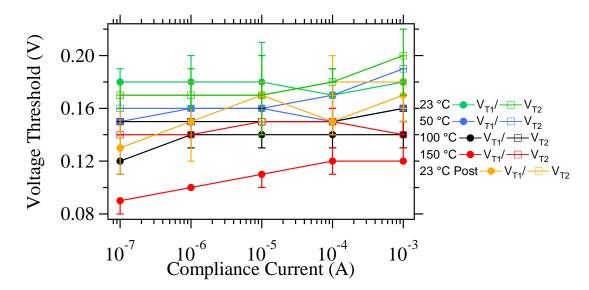

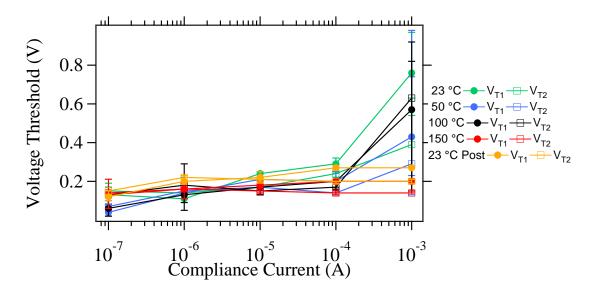

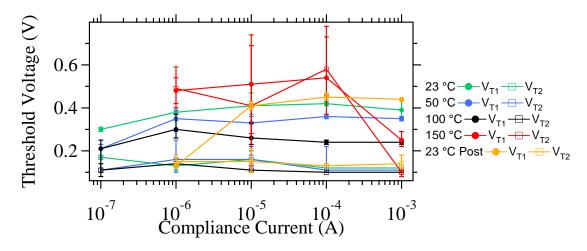

The Sb<sub>2</sub>Se<sub>3</sub>-layered device threshold voltages at each temperature and programming compliance current for the first write (on a virgin device) and the second write (post a single write/erase cycle) are shown in Figure 3.2. Typical values are listed in Table 3.1. Five to six virgin devices were tested at each compliance current and temperature. Post 150 °C, devices remained on the probe station and were allowed to cool over night. The devices were tested approximately 17 hours post 150 °C thermal exposure. Bars above and below the average points provided in Figure 3.2 are the high and low threshold voltage values, not error bars.

Figure 3.2: Average Write Threshold Voltages of Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Stack Devices versus the Programming Compliance Current at Four Different Temperatures.

| Programming<br>Current | $23 \ ^{\circ}C \ V_{T1}/V_{T2} \ (V)$ | $50 \ ^{\circ}C$<br>V <sub>T1</sub> /V <sub>T2</sub><br>(V) | $100 \ ^{\circ}C$<br>V <sub>T1</sub> /V <sub>T2</sub><br>(V) | 150 °C<br>V <sub>T1</sub> /V <sub>T2</sub><br>(V) | $23 \ ^{\circ}C \ Post$ $V_{T1}/V_{T2}$ $(V)$ |

|------------------------|----------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------|

| 100 nA                 | 0.31/0.22                              | 0.28/0.20                                                   | 0.24/0.19                                                    | 0.21/0.20                                         | 0.27/0.21                                     |

| 1 μΑ                   | 0.31/0.21                              | 0.30/0.19                                                   | 0.25/0.19                                                    | 0.21/0.20                                         | 0.26/0.21                                     |

| 10 µA                  | 0.32/0.21                              | 0.29/0.19                                                   | 0.25/0.20                                                    | 0.21/0.18                                         | 0.26/0.20                                     |

| 100 µA                 | 0.31/0.21                              | 0.28/0.20                                                   | 0.24/0.19                                                    | 0.21/0.17                                         | 0.26/0.19                                     |

| 1 mA                   | 0.31/0.21                              | 0.28/0.20                                                   | 0.25/0.19                                                    | 0.21/0.15                                         | 0.26/0.21                                     |

Table 3.1: Average Threshold Voltage Values for Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Device at Five

Different Programming Currents and Four Different Temperatures.

The compliance current had no effect on the threshold voltage as seen by the horizontal lines of Figure 3.2. However, the devices programmed at 150 °C have a slight decrease in  $V_{T2}$  after 1  $\mu$ A programming current whereas  $V_{T1}$  remains constant.

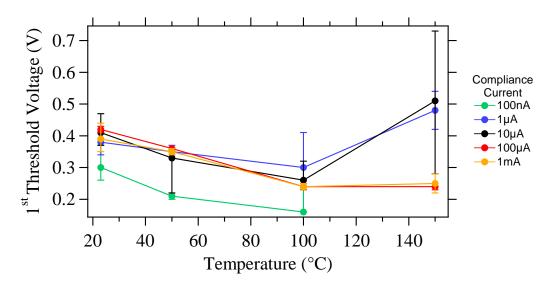

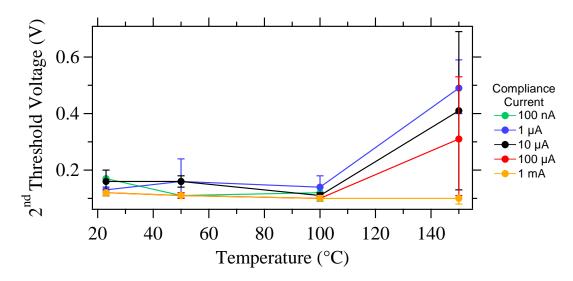

The first and second threshold voltages versus temperature are shown in Figure

3.3 and Figure 3.4, respectively.

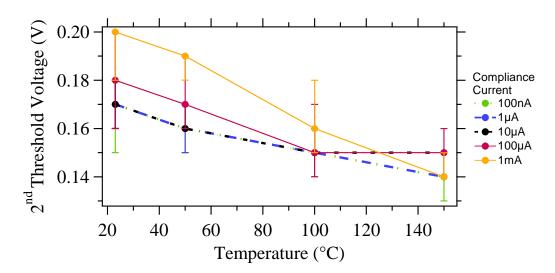

Figure 3.3: First Threshold Voltages of Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Stack Devices versus Temperature for Five Different Programming Compliance Currents.

Figure 3.4: Second Threshold Voltages for Ge<sub>2</sub>Se<sub>3</sub>/Sb<sub>2</sub>Se<sub>3</sub>/Ag Stack Devices versus Temperature for Five Different Programming Compliance Currents.

The  $V_{T1}$  of the Sb<sub>2</sub>Se<sub>3</sub> devices decrease with increase in temperature as seen in Figure 3.3. This is consistent for thermal energy entering the system and yields an

activation energy of 0.032 eV. Within each temperature regime, all programming currents yielded  $V_{T1}$  values within 20 mV of each other as seen in Table 3.1. At 150 °C, the  $V_{T1}$  values differ by up to 50 mV, which indicates some other phenomena is happening at the elevated temperature.

The V<sub>T2</sub> seen in Figure 3.4 are much less affected by temperature than the V<sub>T1</sub>. However, at 150 °C, the temperature appears to have a greater effect on the V<sub>T2</sub>, as seen by the slope of the line from 100 °C to 150 °C. Overall, the V<sub>T2</sub> are less than the V<sub>T1</sub>. The V<sub>T2</sub> being less than the V<sub>T1</sub> suggests that the channel was formed on the first write and on subsequent writes the Ag moves in the same pathway as formed in the first write cycle (6). The electric field at the threshold voltage at 23 °C is 2 x 10<sup>4</sup> Vcm<sup>-1</sup>.

The 23 °C post thermal exposure threshold voltages are listed in Table 3.1. Thermal exposure at 150 °C for 90 minutes lowered  $V_{T1}$  by 40-60 mV. This could be due to structural relaxation of the Ge<sub>2</sub>Se<sub>3</sub> (16).  $V_{T2}$  was virtually unaffected by the thermal exposure with most devices having a 23 °C post thermal value of 0.21 V, the same  $V_{T2}$  for pre thermal exposure 23 °C.

#### $3.2.2 \underline{Ge_2Se_3/SnSe/Ag}$