# DESIGN GUIDE FOR CMOS PROCESS ON-CHIP 3D INDUCTOR

## USING THRU-WAFER VIAS

By

Gary VanAckern

A thesis

submitted in partial fulfillment

of the requirements for the degree of

Master of Science in Electrical Engineering

Boise State University

May 2011

## BOISE STATE UNIVERSITY GRADUATE COLLEGE

## **DEFENSE COMMITTEE AND FINAL READING APPROVALS**

of the thesis submitted by

Gary VanAckern

Thesis Title: Design Guide For CMOS Process On-Chip 3D Inductor Using Thruwafer Vias

Date of Final Oral Examination: 09 March 2011

The following individuals read and discussed the thesis submitted by student Gary VanAckern, and they evaluated his presentation and response to questions during the final oral examination. They found that the student passed the final oral examination.

| R. Jacob Baker, Ph.D. | Chair, Supervisory Committee  |

|-----------------------|-------------------------------|

| Amy Moll, Ph.D.       | Member, Supervisory Committee |

| Vishal Saxena, Ph.D.  | Member, Supervisory Committee |

The final reading approval of the thesis was granted by R. Jacob Baker, Ph.D., Chair of the Supervisory Committee. The thesis was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College.

#### ACKNOWLEDGEMENTS

It has been a great honor and privilege to complete my Masters of Science Degree in Electrical Engineering (MSEE) at Boise State University (BSU).

First of all, I would like to thank my advisor, Dr. Jake Baker, who has provided me with countless hours of quality instruction, guidance, and motivation to complete this thesis. I thank Dr. Saxena for his encouragement and continued support while attending BSU.

I would like to extend a special thanks to Dr. Amy Moll for accepting me to work on the Darpa research project at BSU. This support provided the core funding for the 3D Thru-Wafer Interconnect (TWI) research and provided the opportunity for my research. Additional thanks goes to Research Triangle Inc (RTI) for fabricating the devices in their silicon process.

I also would like to thank my close friend Claude R. Swarthout whose friendship spurred me to attend graduate school. At the same time, I would be very remiss had I not expressed my sincere gratitude to my extremely supportive wife and daughter for the many hours spent away from home while completing this program. Finally, I would like to thank my parents for everything that parent's do that they never get credit for.

## ABSTRACT

Three-dimensional (3D) inductors using high aspect ratio (10:1) thru-wafer via (TWV) technology in a complementary metal oxide semiconductor (CMOS) process have been designed, fabricated, and measured. The inductors were designed using 500 $\mu$ m tall vias with the number of turns ranging from 1 to 20 in both a wide and narrow trace width to space ratios. Radio frequency characterization was studied with emphasis upon de-embedding techniques and resulting effects. The open, short, thru de-embedding (OSTD) technique was used to measure all devices. The highest quality factor (Q) measured was 11.25 at 798MHz for a 1-turn device with a self-resonant frequency (f<sub>sr</sub>) of 4.4GHz. The largest inductance (L) measured was 45nH on a 20-turn wide trace device with a maximum Q of 4.25 at 732MHz. A 40% reduction in area is achieved by exploiting the TWV technology when compared to planar devices. This technology shows promising results with further development and optimization.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                            | iv   |

|---------------------------------------------|------|

| ABSTRACT                                    | v    |

| LIST OF TABLES                              | ix   |

| LIST OF FIGURES                             | X    |

| LIST OF ABBREVIATIONS                       | xiii |

| LIST OF SYMBOLS                             | XV   |

| CHAPTER 1 – INTRODUCTION                    | 1    |

| 1.1 Background                              | 1    |

| 1.2 Motivation                              | 2    |

| 1.3 Thesis Organization                     | 3    |

| CHAPTER 2 – INDUCTOR PHYSICS                | 4    |

| 2.1 The Inductive Phenomena                 | 4    |

| 2.2 Mutual- and Self-Inductance             | 7    |

| 2.3 Skin Effect                             | 10   |

| CHAPTER 3 – MONOLITHIC CMOS PLANER INDUCTOR | 16   |

| 3.1 Inductor Architectures                  | 16   |

| 3.2 Modeling the Planar Inductor            | 20   |

| The Physical Model                          | 21   |

| CHAPTER 4 – PARAMETER CALCULATION           | 27   |

| 4.1 Inductance (L) Calculation                                   | 27 |

|------------------------------------------------------------------|----|

| 4.2 Series Resistance (R <sub>S</sub> ) Calculation              | 31 |

| 4.3 Feed-Thru Capacitance (C <sub>P</sub> ) Calculation          | 33 |

| 4.4 Oxide Capacitance (C <sub>OX</sub> ) Calculation             | 34 |

| 4.5 Silicon Resistance ( $R_{Si}$ ) and Capacitance ( $C_{Si}$ ) | 34 |

| 4.6 Quality Factor (Q) Calculation                               | 37 |

| 4.7 Self-Resonant Frequency (f <sub>SR</sub> ) Extraction        | 39 |

| CHAPTER 5 – 3D INDUCTOR                                          | 41 |

| 5.1 Architecture                                                 | 41 |

| 5.2 3D Inductor Fabrication                                      | 44 |

| The Process Flow                                                 | 45 |

| CHAPTER 6 – MEASUREMENT TECHNIQUE                                | 58 |

| 6.1 Equipment Setup                                              | 58 |

| 6.2 Equipment Calibration                                        | 59 |

| 6.3 Parasitic De-Embedding                                       | 62 |

| 6.4 A 3D Measurement Pitfall                                     | 72 |

| CHAPTER 7 – 3D TWV INDUCTOR MEASURED PERFORMANCE                 | 73 |

| 7.1 Smith Chart Measured S11                                     | 73 |

| 7.2 Measured Quality Factor (Q)                                  | 76 |

| 7.3 Measured Self-Resonant Frequency $(f_{SR})$                  | 78 |

| 7.4 Measured Inductance (L) vs. Frequency                        | 79 |

| 7.5 Measured  Z  vs. Frequency                                   | 82 |

| 7.6 Measured Z (Phase Angle) vs. Frequency                       | 84 |

| 7.7 Line Trace Width to Line Space Ratio   |

|--------------------------------------------|

| 7.8 Via Height 87                          |

| 7.9 Via Size and Via-to-Via Pitch 87       |

| 7.10 Surface Trace Lengths                 |

| 7.11 Inductor Radius 88                    |

| CHAPTER 8 – SUMMARY AND CONCLUSIONS        |

| BIBLIOGRAPHY 91                            |

| APPENDIX A                                 |

| Smith Chart Tutorial                       |

| APPENDIX B                                 |

| Measured and Calculated Data – All Devices |

| APPENDIX C114                              |

| Software Written to Support Thesis         |

# LIST OF TABLES

| Table B.1 | Wide Trace Wire Groups Inductor Length vs. N <sub>Turns</sub>       |

|-----------|---------------------------------------------------------------------|

| Table B.2 | Narrow Trace Wire Groups Inductor Length vs. N <sub>Turns</sub> 113 |

| Table B.3 | Wide Trace Wire Groups $\eta_{dut}$ vs. $N_{Turns}$ 114             |

| Table B.4 | Narrow Trace Wire Groups $\eta_{du}t$ vs. $N_{Turns}$               |

# LIST OF FIGURES

| Figure 2.1 | Magnetic Flux of a Current Carrying Wire Segment                           | 4  |

|------------|----------------------------------------------------------------------------|----|

| Figure 2.2 | Total Magnetic Flux Through a Surface                                      | 6  |

| Figure 2.3 | Mutual-Inductance of Two Coils                                             | 7  |

| Figure 2.4 | Mutual-Inductance of Two Coils                                             | 8  |

| Figure 2.5 | Mutual and Self-Inductance of a Planar Spiral Inductor                     | 10 |

| Figure 2.6 | Electric Field vs. Skin Depth                                              | 11 |

| Figure 2.7 | Skin Depth ( $\delta$ ) vs. Frequency                                      | 13 |

| Figure 2.8 | Effective Conductor Thickness $(t_{eff})$ vs. Frequency                    | 14 |

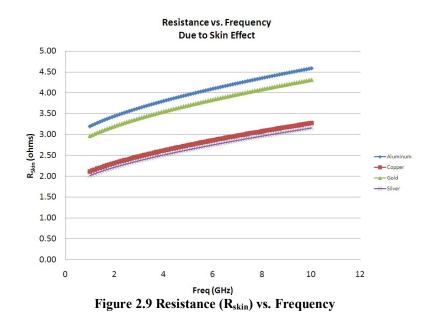

| Figure 2.9 | Resistance (R <sub>skin</sub> ) vs. Frequency                              | 14 |

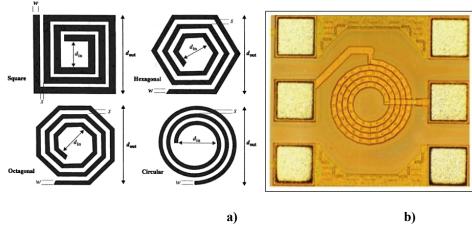

| Figure 3.1 | a) Planar Spiral Inductor Shapes [23], b) Circular Inductor [17]           | 17 |

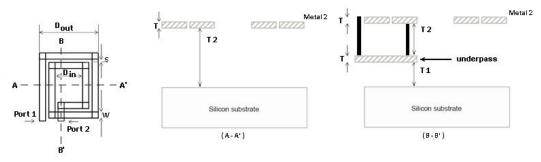

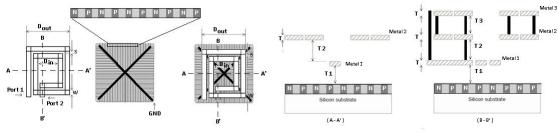

| Figure 3.2 | Layout and Cross-Section of 2 Metal Square Spiral Inductor [21]            | 18 |

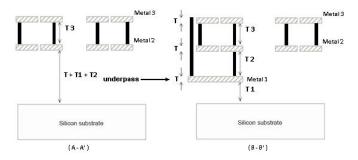

| Figure 3.3 | Cross-Section of Stacked and Shorted Spiral Inductor [21]                  | 19 |

| Figure 3.4 | Layout and Cross-Section of Spiral Inductor with PGS [1, 21]               | 20 |

| Figure 3.5 | Electric and Magnetic Fields in a CMOS Planner Inductor [21]               | 22 |

| Figure 3.6 | Basic Planar Inductor Equivalent Circuit Physical Model<br>[4, 20, 21, 24] | 23 |

| Figure 3.7 | Inductor Sub-Models [4, 20, 21, 24]                                        | 24 |

| Figure 3.8 | Substrate Coupling with and without PGS [21]                               | 24 |

| Figure 3.9 | Basic Planar Inductor Equivalent Circuit Physical Model with PGS [21]      | 25 |

| Figure 4.1  | Greenhouse Method [7, 11]                                                              | 29 |

|-------------|----------------------------------------------------------------------------------------|----|

| Figure 4.2  | Reflected Image [24, 5]                                                                | 31 |

| Figure 4.3  | Modes of Operation Circuit Diagrams [26]                                               | 36 |

| Figure 4.4  | Modes of Operation [26]                                                                | 37 |

| Figure 4.5  | Q and  Z                                                                               | 40 |

| Figure 5.1  | HFSS 3D Inductor Architecture                                                          | 42 |

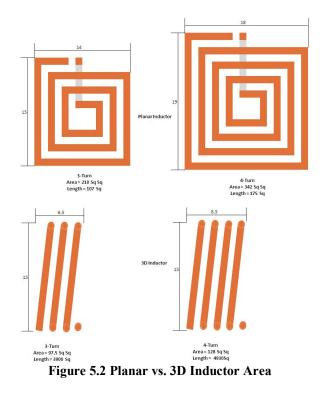

| Figure 5.2  | Planar vs. 3D Inductor Area                                                            | 43 |

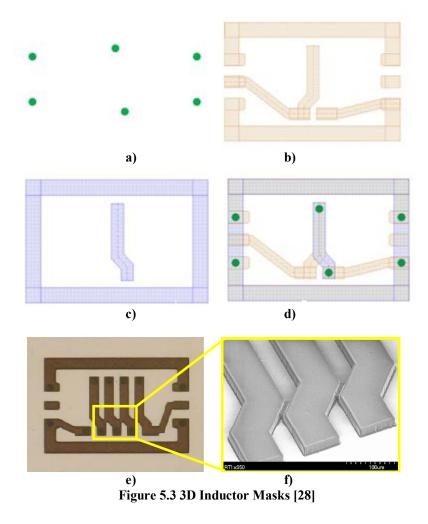

| Figure 5.3  | 3D Inductor Masks [28]                                                                 | 46 |

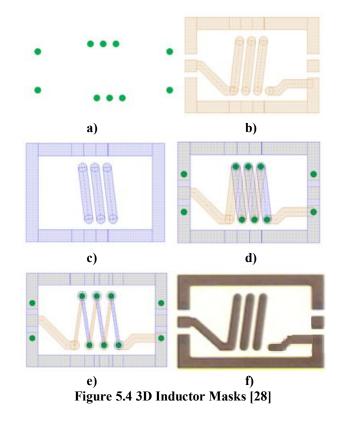

| Figure 5.4  | 3D Inductor Masks [28]                                                                 | 47 |

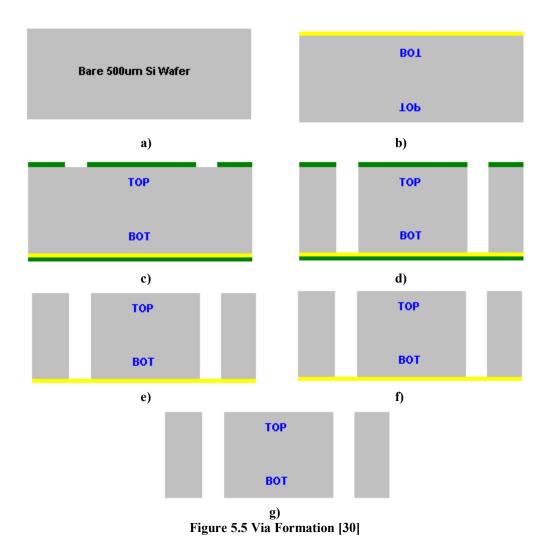

| Figure 5.5  | Via Formation [30]                                                                     | 49 |

| Figure 5.6  | Via Profile with Oxide Charge Buildup [30]                                             | 50 |

| Figure 5.7  | Parylene CVD Process Flow [30]                                                         | 52 |

| Figure 5.8  | Barrel Coating Method [34]                                                             | 54 |

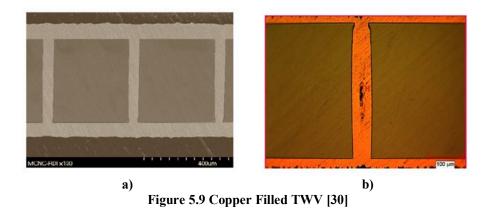

| Figure 5.9  | Copper Filled TWV [30]                                                                 | 55 |

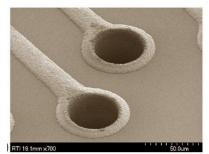

| Figure 5.10 | SEM of Barrel Coated TWV [30]                                                          | 55 |

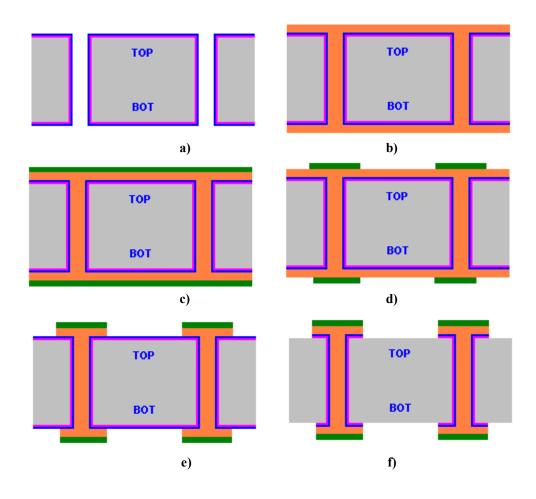

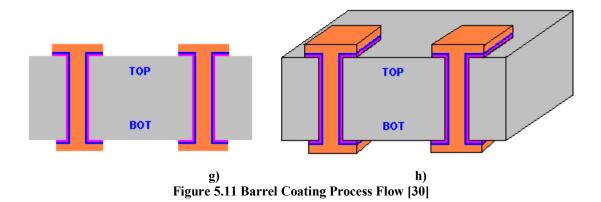

| Figure 5.11 | Barrel Coating Process Flow [30]                                                       | 57 |

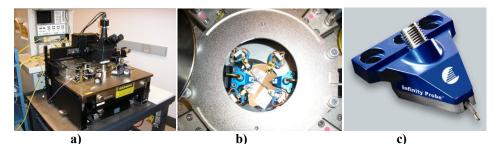

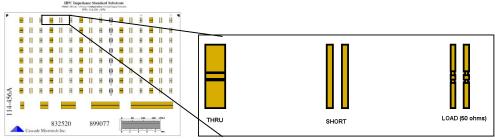

| Figure 6.1  | a) Cascade <sup>™</sup> Microtech Probe Station, b) Top-hat View,<br>c) GSG Probe [37] | 59 |

| Figure 6.2  | Impedance Standard Substrate (ISS) [40]                                                | 61 |

| Figure 6.3  | Infinity Probe <sup>™</sup> Skating [38]                                               | 61 |

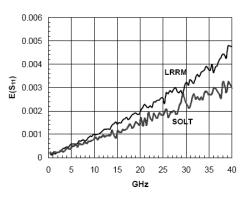

| Figure 6.4  | Calibration Error by Method [38]                                                       | 62 |

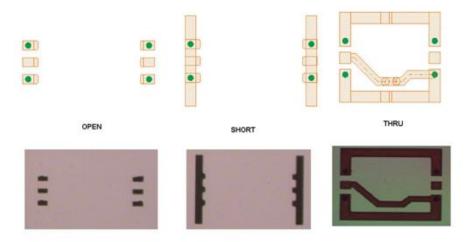

| Figure 6.5  | On-Wafer De-Embedding Structures                                                       | 63 |

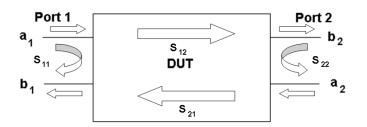

| Figure 6.6  | 2-Port S-Parameter Measurement Block Diagram                                           | 64 |

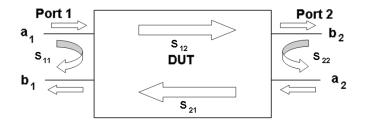

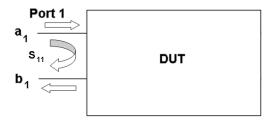

| Figure 6.7  | 1-Port S-Parameter Measurement Block Diagram                                                 | 65 |

|-------------|----------------------------------------------------------------------------------------------|----|

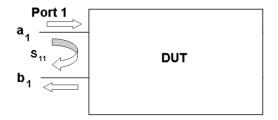

| Figure 6.8  | OPD De-Embedding vs. Q and $F_{sr}$                                                          | 66 |

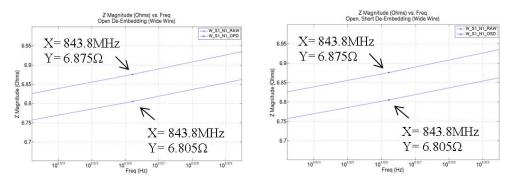

| Figure 6.9  | Z  vs. OPD and OSD De-Embedding                                                              | 68 |

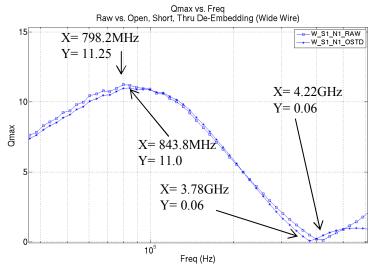

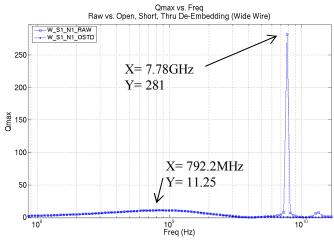

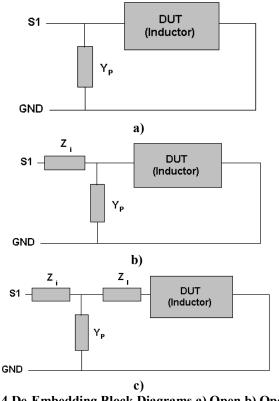

| Figure 6.10 | OSTD De-Embedding for Q <sub>max</sub> vs. Frequency                                         | 69 |

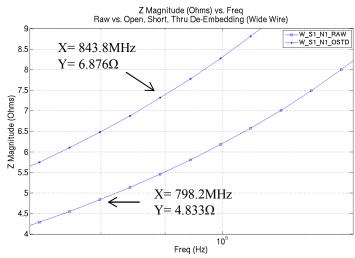

| Figure 6.11 | OSTD De-Embedding for $ Z $ vs. Frequency                                                    | 70 |

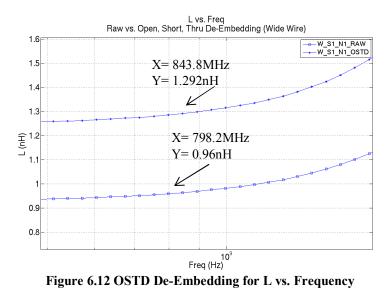

| Figure 6.12 | OSTD De-Embedding for L vs. Frequency                                                        | 70 |

| Figure 6.13 | OSTD De-Embedding for Q <sub>max</sub> vs. Frequency                                         | 71 |

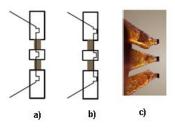

| Figure 6.14 | De-Embedding Block Diagrams: a) Open, b) Open-Short,<br>c) Open-Short-Thru [39]              | 71 |

| Figure 6.15 | Auxiliary Chuck                                                                              | 72 |

| Figure 6.16 | Auxiliary Chuck Micrograph                                                                   | 72 |

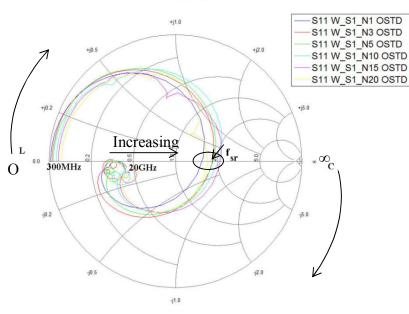

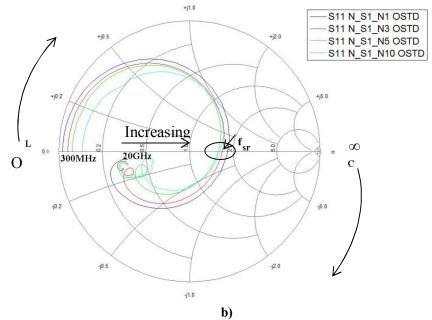

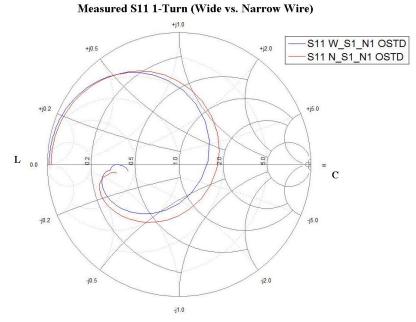

| Figure 7.1  | a) Measured S <sub>11</sub> for WT, b) Measured S <sub>11</sub> NT Devices for N=1, 3, 5, 10 | 75 |

| Figure 7.2  | Measured $S_{11}$ for WT and NT Devices for N=1                                              | 75 |

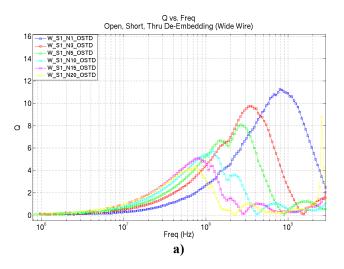

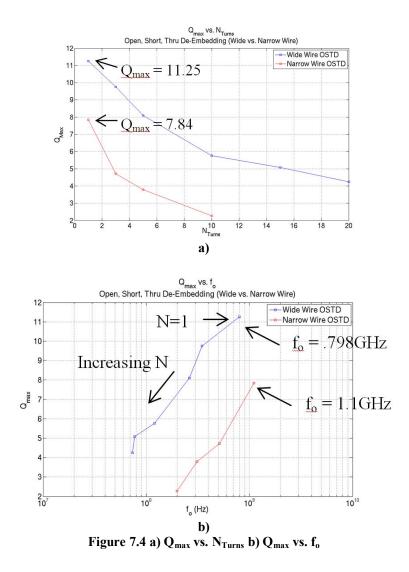

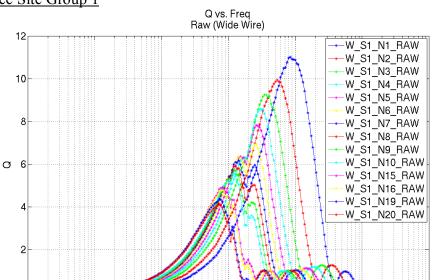

| Figure 7.3  | a) Q vs. Frequency for WT, b) Q vs. Frequency NT Devices (1, 3, 5, 10, {15, 20})             | 77 |

| Figure 7.4  | a) Q <sub>max</sub> vs. N <sub>Turns</sub> ,b) Q <sub>max</sub> vs. f <sub>o</sub>           | 78 |

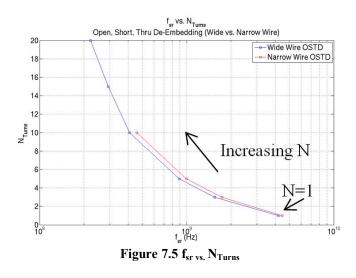

| Figure 7.5  | f <sub>sr</sub> vs. N <sub>Turns</sub>                                                       | 79 |

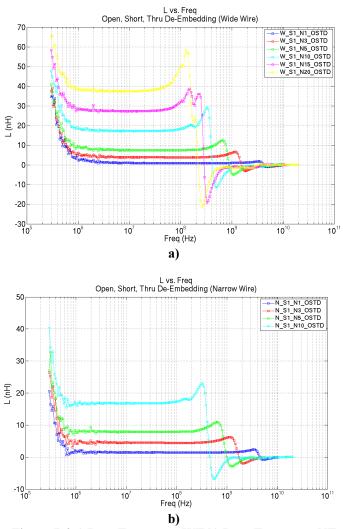

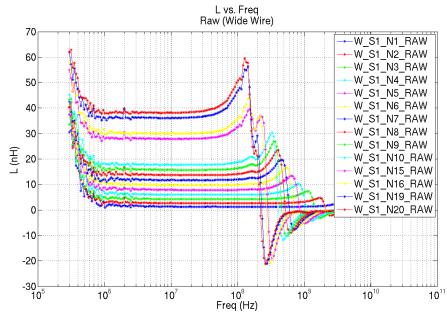

| Figure 7.6  | a) L vs. Frequency WT, b) L vs. Frequency NT                                                 | 80 |

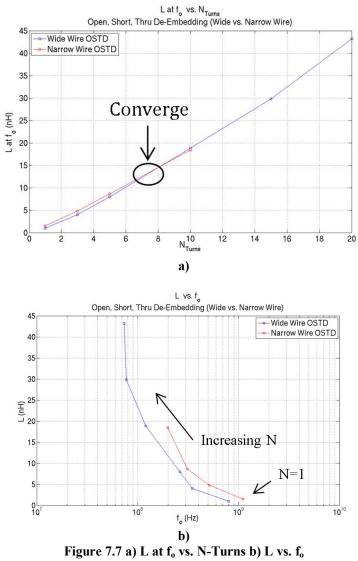

| Figure 7.7  | a) L at f <sub>o</sub> vs. N-Turns, b) L vs. f <sub>o</sub>                                  | 81 |

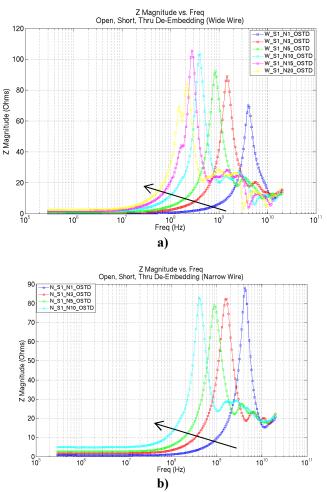

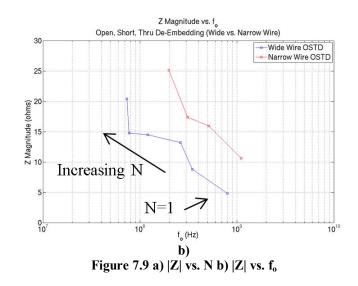

| Figure 7.8  | a) $ Z $ vs. Frequency WT, b) $ Z $ vs. Frequency NT                                         | 82 |

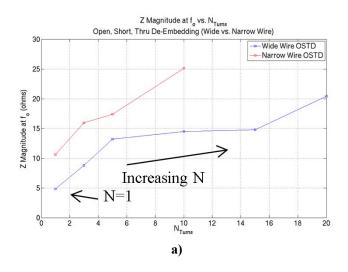

| Figure 7.9  | a) $ Z $ vs. N, b) $ Z $ vs. $f_o$                                                           | 84 |

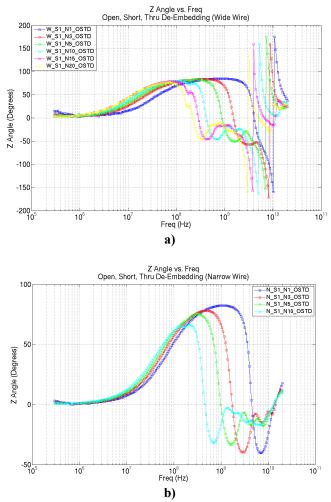

| Figure 7.10 | a) Z Angle vs. Frequency WT, b) Z Angle vs. and Frequency NT                                 | 85 |

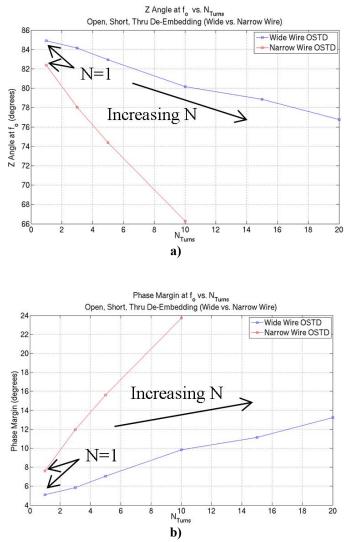

| Figure 7.11 | a) Z Angle vs. N <sub>Turns</sub> , b) Phase Margin at f <sub>o</sub> vs. N <sub>Turns</sub> | 86 |

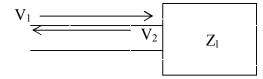

| Figure A.1  | Incident and Reflected Wave from a Load                 |

|-------------|---------------------------------------------------------|

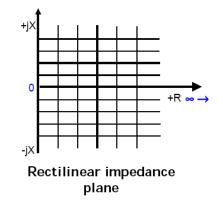

| Figure A.2  | Rectilinear Impedance Plane (Complex)                   |

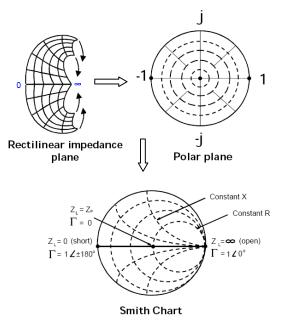

| Figure A.3  | Smith Chart from Rectilinear Plane and Polar Plane      |

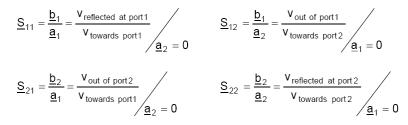

| Figure A.4  | 2-Port Scattering Parameter Coefficients [43]101        |

| Figure A.5  | 2-Port Measurement                                      |

| Figure A.6  | 1-Port Measurement                                      |

| Figure B.1  | Q vs. Frequency Wide Trace Site Group 1104              |

| Figure B.2  | L vs. Frequency Wide Trace Site Group 1104              |

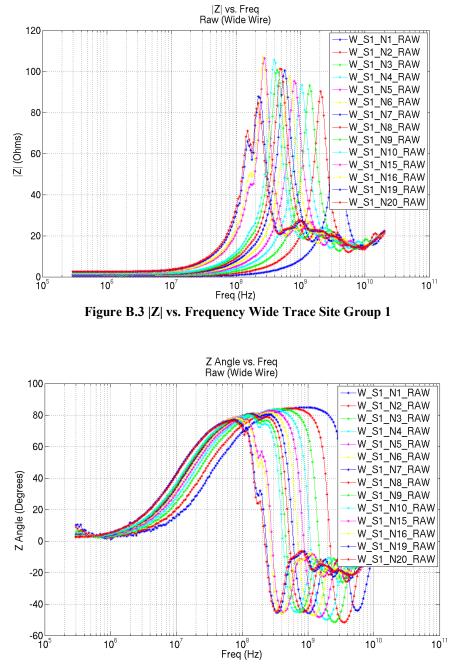

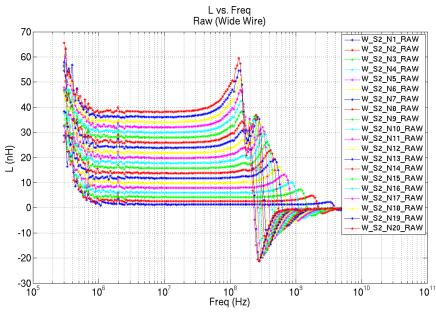

| Figure B.3  | Z  vs. Frequency Wide Trace Site Group 1105             |

| Figure B.4  | Z Phase Angle vs. Frequency Wide Trace Site Group 1105  |

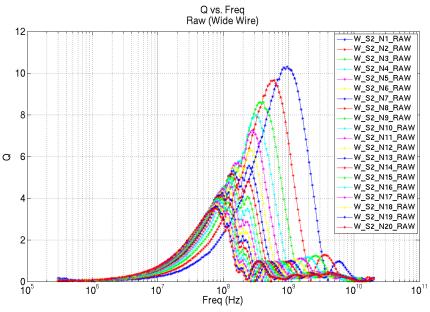

| Figure B.5  | Q vs. Frequency Wide Trace Site Group 2106              |

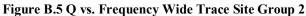

| Figure B.6  | L vs. Frequency Wide Trace Site Group 2106              |

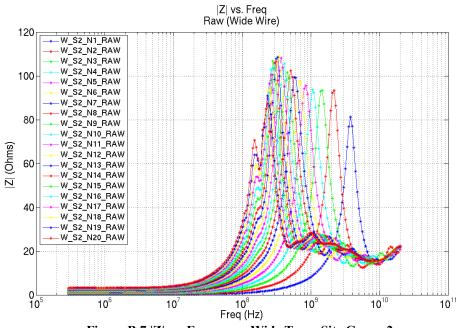

| Figure B.7  | Z  vs. Frequency Wide Trace Site Group 2107             |

| Figure B.8  | Z Phase Angle vs. Frequency Wide Trace Site Group 2107  |

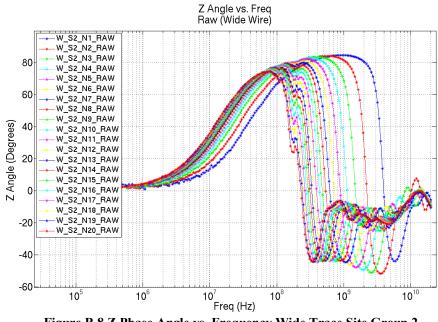

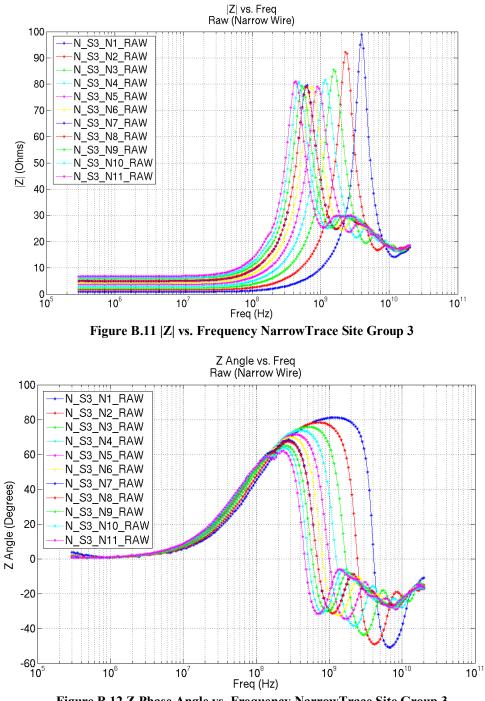

| Figure B.9  | Q vs. Frequency NarrowTrace Site Group 3108             |

| Figure B.10 | L vs. Frequency NarrowTrace Site Group 3108             |

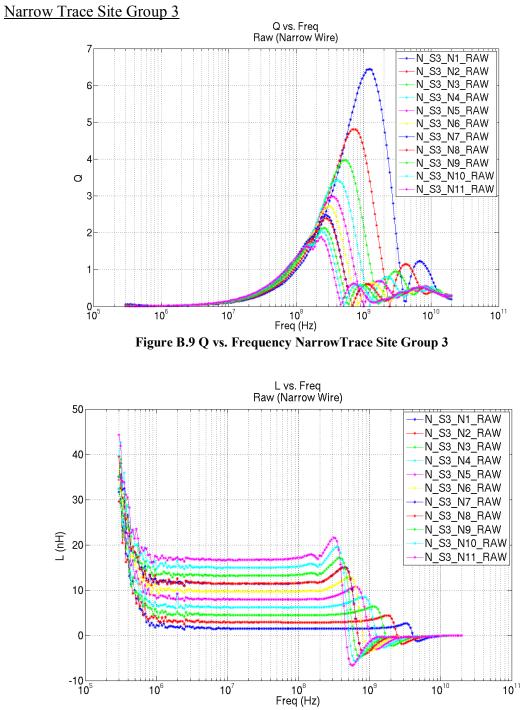

| Figure B.11 | Z  vs. Frequency NarrowTrace Site Group 3109            |

| Figure B.12 | Z Phase Angle vs. Frequency NarrowTrace Site Group 3109 |

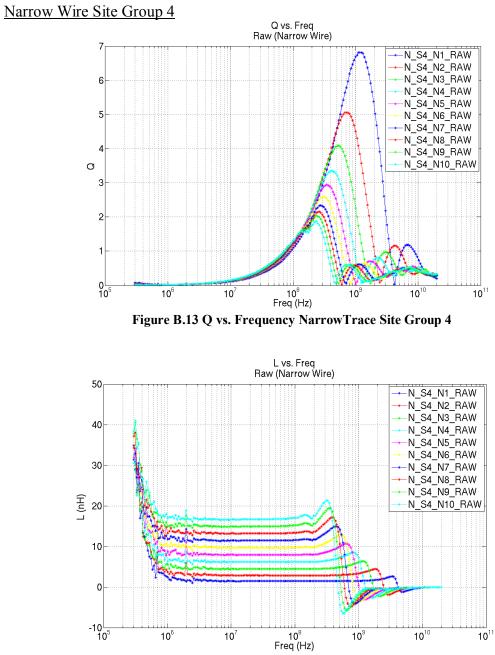

| Figure B.13 | Q vs. Frequency NarrowTrace Site Group 4110             |

| Figure B.14 | L vs. Frequency NarrowTrace Site Group 4110             |

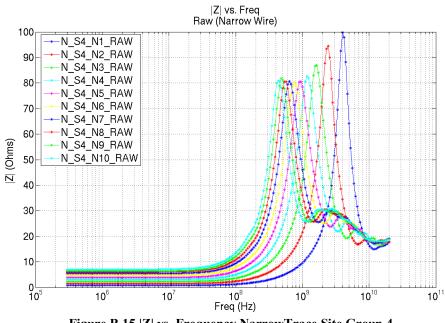

| Figure B.15 | Z  vs. Frequency NarrowTrace Site Group 4111            |

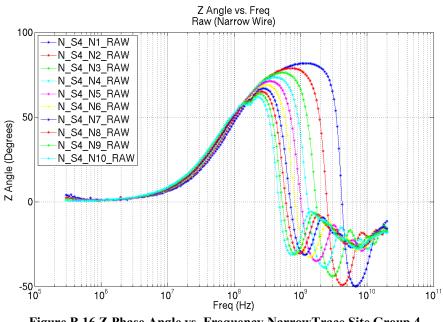

| Figure B.16 | Z Phase Angle vs. Frequency NarrowTrace Site Group 4111 |

# LIST OF ABBREVATIONS

| AC       | Alternating Current.                               |

|----------|----------------------------------------------------|

| BSU      | Boise State University.                            |

| BW       | Bandwidth.                                         |

| CMOS     | Complimentary Metal-Oxide Semi-Conductor.          |

| CVD      | Chemical Vapor Deposition.                         |

| CV0      | Voltage-Controlled Oscillator.                     |

| DB       | Decibels.                                          |

| DQTM     | Dielectric Quasi-TEM Mode.                         |

| DRI      | Deep Reactive-Ion.                                 |

| DUT      | Device Under Test.                                 |

| EMF      | Electro-Magnetic Force.                            |

| FEA      | Finite Element Analysis.                           |

| GPIB     | General Purpose Interface Bus.                     |

| GSG      | Ground-Signal-Ground.                              |

| HFSS     | High-Frequency Simulation Solver.                  |

| IEEE-488 | Institute of Electrical and Electronics Engineers. |

| ISS      | Impedance-Sub-Strate.                              |

| LNA      | Low-Noise Amplifier.                               |

| LRM      | Load-Reflection-Match.                             |

| LRRM     | Load-Reflection-Match-Match.                       |

| MCNC     | Microelectronics Center of North Carolina.         |

| MMIC     | Micro-Machined Integrated Circuit.                 |

| MOCVD    | Metal Organic Chemical Vapor Deposition.           |

| NT       | Narrow-Trace.                                      |

| OPD      | Open-De-embedding.                                 |

| OSD      | Open-Short De-embedding.                           |

| OSTD     | Open-Short-Thru De-embedding.                      |

| PGS              | Patterned Ground Shield.        |

|------------------|---------------------------------|

| RF               | High Frequency.                 |

| RLC              | Resistive-Inductive-Capacitive. |

| SEM <sub>1</sub> | Skin-Effect Mode.               |

| SEM <sub>2</sub> | Scanning Electron Microscope.   |

| SOLT             | Short-Open-Load-Thru.           |

| SWM              |                                 |

| TiN              | Titanium Nitride.               |

| TRL              |                                 |

| TWV              |                                 |

| U.S              | United States.                  |

| WT               |                                 |

| 3D               |                                 |

|                  |                                 |

# LIST OF SYMBOLS

| AMD               | Arithmetic Mean Distance.                      |

|-------------------|------------------------------------------------|

| Α                 | Area.                                          |

| A <sub>sw</sub>   | Side-Wall Area.                                |

| GHz               | Giga-Hertz.                                    |

| GMD               | Geometric Mean Distance.                       |

| G <sub>si</sub>   | Silicon Conductance.                           |

| HF                | High Frequency.                                |

| Hz                |                                                |

| C                 | Capacitance.                                   |

| C <sub>shld</sub> | Capacitance with Patterned Ground Shield.      |

| C <sub>ox</sub>   | Oxide Capacitance.                             |

| Ср                | Parallel (Feed-Thru) Capacitance.              |

| C <sub>si</sub>   | Silicon Self-Capacitance.                      |

| C <sub>sw</sub>   | Side-Wall Capacitance.                         |

| C <sub>up</sub>   | Underpass Capacitance.                         |

| D <sub>avg</sub>  | Average Distance.                              |

| D <sub>in</sub>   | Planar Inductor Inside Distance.               |

| D <sub>out</sub>  | Planar Inductor Outside Distance.              |

| d                 | Distance.                                      |

| f                 | Frequency.                                     |

| f <sub>o</sub>    | Characteristic Frequency at Q <sub>max</sub> . |

| f <sub>sr</sub>   | Self-Resonant Frequency.                       |

| Imag()            | Imaginary Part.                                |

| L                 | Inductance.                                    |

| L <sub>i</sub>    |                                                |

| 1                 | Inductor Length.                               |

| l <sub>fix</sub>          | Fixture Length.                             |

|---------------------------|---------------------------------------------|

| l <sub>dut</sub>          | DUT Length.                                 |

| M <sub>i</sub>            |                                             |

| M <sub>i,j</sub>          | Mutual Inductance Between i and j.          |

| N                         | Number of Turns.                            |

| n                         | Number of Turns over the Underpass.         |

| nH                        | Nano-Henries.                               |

| рН                        | Pico-Henries.                               |

| Q                         | Quality Factor.                             |

| Q <sub>max</sub>          | Maximum Quality Factor.                     |

| R                         | Resistance.                                 |

| Real()                    | Real Part.                                  |

| R <sub>s</sub>            | Series Resistance.                          |

| R <sub>si</sub>           | Silicon Resistance.                         |

| SF <sub>4</sub>           | Sulfur Tetraflouride.                       |

| S-Parameters              | Scattering Parameters.                      |

| S <sub>ij</sub>           | Scattering Parameters Between Port i and j. |

| Τ                         | Frequency Correction Factor.                |

| t                         | Metal Thickness.                            |

| t <sub>eff</sub>          | Effective Metal Thickness.                  |

| t <sub>ox,m1-m2</sub> Oxi | de Thickness Between Metal Layers 1 and 2.  |

| w                         | Metal Trace Width.                          |

| Y <sub>ij</sub>           | Admittance in Terms of Port i and j.        |

| Y <sub>p</sub>            | Parallel Admittance.                        |

| Z <sub>ij</sub>           | Impedance Between Ports i and j.            |

| Z <sub>1</sub>            | Impedance of the Load.                      |

| Z <sub>o</sub>            | Characteristic Impedance(50Ω).              |

| Γ                         | Reflection Coefficient.                     |

| δ                         | Skin Depth.                                 |

| η <sub>dut</sub>          | Proportion of DUT to Fixture.               |

| Ω               | Ohms.                                    |

|-----------------|------------------------------------------|

| ε               | Permittivity.                            |

| ε <sub>0</sub>  | Permittivity in Free Space.              |

| ε <sub>ox</sub> | Oxide Permittivity.                      |

| ε <sub>r</sub>  | Relative Permittivity.                   |

| Φ <sub>m</sub>  | Total Magnetic Flux.                     |

| σ               | Conductivity.                            |

| π               |                                          |

| μ               | Permeability.                            |

| μ <sub>0</sub>  | Permeability in Free Space.              |

| μ <sub>r</sub>  | Relative Permeability.                   |

| ω               | Frequency in Terms of PI.                |

| ω <sub>0</sub>  | Characteristic Frequency in Terms of PI. |

| Z               |                                          |

#### **CHAPTER 1 - INTRODUCTION**

#### 1.1 Background

The interest and proliferation of radio-frequency (RF) circuits in recent years has provided broad opportunity for development of front-end RF modules such as the voltage-controlled oscillator (VCO), low-noise assembly (LNA), transformer, filter, and regulator to support a multitude of new wireless applications [1, 2]. These RF modules have had their foundation built upon discrete passive circuit components like the high frequency (HF) inductor. In the last decade, integration of monolithic inductors built in silicon-based complementary metal oxide semiconductors (CMOS) has been realized rather than relying on their predecessor off-chip components [3]. CMOS has shown itself to be the most preferred technology due to the aggressive scaling in MOS devices and its improved performance above 1GHz [4, 5]. Multi-mode wireless technology also looks to utilize high quality CMOS inductors [50].

As devices scale, designers are challenged with producing smaller and more efficient modules while maintaining or improving circuit performance, predictability, and robustness [2]. These three design requirements directly transcend to the passive components that make up the modules and thus have fueled the quest for a much improved integrated inductor.

### **1.2 Motivation**

While the inductive coil has been around for nearly 200 years, its wide-spread use in modern silicon-based CMOS circuits has been limited by its relatively large size (when compared to other circuit elements) and its inherent performance and integration limitations.

In order to achieve a reasonable inductance value (~10nH), the device needs to be designed and manufactured with an extremely large footprint, on the order of 250um<sup>2</sup>. This factor alone is why most inductors are forced to be implemented off-chip. This becomes apparent in CMOS technology since increasing the inductor size both increases the manufacturing cost and produces undesired parasitic effects. Device integration is limited mostly by manufacturing process maturity while parasitic effects reduce the fundamental performance factors of an inductor. This includes a poor quality factor (Q), a reduction in self-resonant frequency ( $f_{sr}$ ), and a low inductance value (L). Due to these issues, several works in recent years have focused on identifying new processing techniques and understanding how the underlying parasitics are limiting the performance of CMOS-based inductors [3]. By having this understanding in hand, circuit designers will be able to optimize and further experiment with new design solutions to achieve a better integrated inductor. This paper provides a starting point for an alternative inductor design: the 3D inductor using through-wafer via interconnects (TWV).

#### **1.3 Thesis Organization**

This thesis aims to provide insight into the design of a 3D integrated inductor using TWV technology versus the conventional CMOS monolithic inductor. Chapter 2 covers a review of inductor physics based upon the monolithic planer spiral topology in a CMOS process. This discussion will cover the inductive phenomena, mutual- and selfinductance, and discuss previous work regarding the electromagnetic fields present within the monolithic inductor. Chapter 3 will provide a more in-depth discussion on the specific monolithic architectures. Parasitics will be identified and their respective measurement parameters will be discussed. The chapter will round out by assembling the measurement parameters into an equivalent circuit physical model. Chapter 4 will introduce the parameter calculation methods for the equivalent circuit physical model presented in Chapter 3. Chapter 5 will present the underlining 3D inductor architecture and discuss its manufacturing process in general terms. Chapter 6 will briefly review the necessary HF measurement setup, de-embedding techniques and their impact on the accuracy of measured results. Chapter 7 will discuss the measured performance of the 3D device compared to published data on an equivalent monolithic device. Chapter 8 will show the development of an equivalent physical model for the 3D inductor. Chapter 9 will draw conclusions on device performance and discuss possible future work for continued research of the 3D inductor using TWVs.

### **CHAPTER 2 - INDUCTOR PHYSICS**

This chapter will briefly review the inductive phenomena as it relates to conducting wires and coil inductors. A brief discussion of the following concepts will also be covered: mutual- vs. self-inductance, and the skin effect.

### 2.1 The Inductive Phenomena

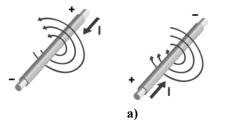

Whether considering a straight wire, a simple coil of wound wire (solenoid), or a CMOS monolithic planar spiral inductor, when an alternating current (AC) source is applied at one terminal of a two terminal device, with the other terminal grounded, an electric current propagates back and forth through the conducting material. The current flow gives rise to a magnetic field intensity (H) and is measured in units of A/m. The alternating nature of the H with change in current direction is shown in Figure 2.1a-b.

Figure 2.1 Magnetic Flux of a Current Carrying Wire Segment

b)

The magnetic field intensity is related to the magnetic flux density (B) as seen below in Equation (2.0), where  $\mu$  is absolute magnetic permeability ( $\mu$ ). Magnetic flux density carries the units of tesla =  $W_b/m = H-A/m^2$ . In the case of free space, absolute permeability is simply  $\mu_0 = 4\pi \cdot 10^{-7} = 1.257 \cdot 10^{-6}$  (H/m).

$$B = \mu H$$

(2.0)

In the absence of freespace, Equation 2.1 illustrates the change in absolute magnetic permeability. In this case of non-free space, the relative permeability ( $\mu_r$ ) of the introduced material scales the permeability of free space ( $\mu_o$ ). This equation indicates that for a relative permeability  $\mu_r = N > 1$ , the magnetic flux density is N-times greater in the material than it would have been in free space [51].

$$\mu = \mu_r \mu_o (H/m)$$

(2.1)

The magnetic field flux is analogous to electric current flow whereas magnetic flux density is to voltage [52]. Unlike electric fields, magnetic fields can occur outside of material where there is an absence of free flowing electrons.

The magnetic flux ( $\Phi_m$ ), as shown in Equation 2.3, represents the total magnetic flux being equal to the integral of the magnetic flux density over an area of a surface S that intersects the field lines. In the special case of a planar surface, this can be simplified to (2.4) [45], where A is the cross-sectional area of intersecting surface and  $\theta$  is the angle between the surface and the magnetic field lines that extend normal to the flow of current.

$$\Phi_m = \int_S B \cdot dS \qquad (2.3)$$

$$\Phi_m = BA\cos\theta \qquad (2.4)$$

Flux linkage ( $\lambda$ ) represents the total magnetic flux passing through a surface S of a single loop of current carrying wire as seen below in Equations (2.4) and Figure 2.2, where N is the number of loops.

$$\lambda = \Phi_T \cdot \mathbf{N} \quad (2.4)$$

Figure 2.2 Total Magnetic Flux Through A Surface

For the case of two 3 loop tightly wound current carrying wires with the same intersecting surface S, the magnetic flux generated from each loop is passed through both loops. As such, the total magnetic flux linkage is increased by the square of the number of loops N times the magnetic flux of one loop of wire. This is shown below in Equation (2.5) and Figure 2.3 [53].

$$\lambda = \Phi_1 \cdot N^2 \quad (2.5)$$

Figure 2.3 Mutual-Inductance of Two Coils

Inductance is primarily a function of geometric shape. Analagous to capacitors storing electric charge, an inductor stores magnetic energy within the core of its windings where the flux density is greatest. The quantity of inductance can be determined by the ratio of flux linkages to the current that creates the magnetic flux as shown below in Equation (2.6) for the cylindrical  $N_{Loop}$  solenoid shown in Figure 2.2 [53].

$$L = \frac{\lambda}{I} = \frac{\phi_{\rm T} \cdot N}{I} = \frac{\mu \cdot N^2 \cdot \pi \cdot a^2}{h}$$

(2.6)

### 2.2 Mutual- and Self-Inductance

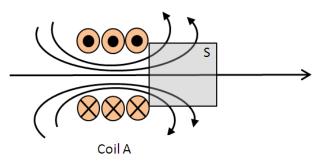

In the same manner as presented in the last section, two types of inductance make up the total inductance: mutual- and self-inductance. Mutual-inductance is a result of the proximity effect occurring between two closely spaced circuits, circuit elements, or wires [21]. This can occur with two elements that are either in series or parallel and depends on the amount of flux linkages interacting between the two elements. Illustrated below in Figure 2.4 are two 3 loop coils of wire with interacting flux linkages. Coil A is being driven by current I<sub>A</sub> and as such is creating the flux density from coil A while coil B is not being driven, but rather receiving. The consequence of coil A on coil B is shown in Equation (2.7). The total flux  $\Phi_{AB}$  from coil A to a single loop of coil B is found by integrating the flux density over the shared surface S. The flux linkages are multiplied by the number of turns N<sub>B</sub> in coil B. The mutual-inductance in Coil B can then be found as shown in Equation (2.8).

Figure 2.4 Mutual-Inductance of Two Coils

$\lambda_{AB} = N_B \cdot \Phi_{AB} \qquad (2.7)$

$$M_{A,B} = \frac{\lambda_{AB}}{I_A} \qquad (2.8)$$

A general Equation (2.9) has been included below for the mutual-inductance of two current carrying 2 loop coils in which both loops are being driven by a current ( $I_A$  and  $I_B$ , respectively). In this case where  $I_A$  and  $I_B$  are equal and flowing in the same direction, the equation simplifies. The total inductance of either loop A or loop B is the summation of all mutual inductances with a net result that can be either positive or negative depending on the direction of current flow.

$$L_{M} = \frac{\lambda_{M_{AB}} \cdot N^{2}}{I_{AB}} = \frac{\lambda_{M_{AB}} \cdot 2^{2}}{I_{AB}} = \frac{M_{Aa}}{I_{A}} + \frac{M_{Ab}}{I_{A}} + \frac{M_{Bb}}{I_{B}} + \frac{M_{Ba}}{I_{B}} = \frac{2 \cdot M_{AB}}{I_{AB}}$$

(2.9)

Self-inductance is a special case of mutual-inductance and is referred to in literature as simply inductance [7]. In this case, rather than two circuit elements, two or more individual wire segments have influence on one another within the same element. Thus, the inductance present is understood to be self-inductance and occurs within its own turns rather than from an outside source. This is shown below in Equation (2.10).

$$L_{AB} = \frac{\lambda_{AB}}{I} = \frac{\phi_{S_{A,B}}}{I} = L_A + L_B$$

(2.10)

The total inductance of a circuit or circuit element is the summation of all mutualand self-inductances with a net result that can be either positive or negative as shown below in Equation (2.11) [7].

$$L_{Total} = \frac{\Phi_{S_{A,B}}}{1} + \frac{\Phi_{M_{A,B}}}{1} = L_A + L_B + 2 \cdot M_{AB}$$

(2.11)

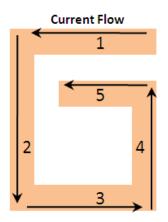

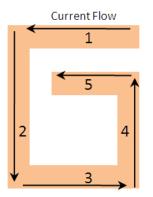

Extending the principles of mutual- and self-inductance to the case of a 1.25 turn monolithic planar spiral inductor as seen below in Figure 2.5, each line segment contributes a self-inductance component. Each line segment pair that has currents traveling in the same direction contribute a positive mutual-inductance term, while line pairs that have opposite direction currents contribute a negative mutual-inductance term. The total inductance is again the summation of all self- and mutual-inductances as shown in Equation (2.12).

Figure 2.5 Mutual- and Self-Inductance of a Planar Spiral Inductor

$$L_{Total} = \frac{\Phi_{S_{A,B}}}{1} + \frac{\Phi_{M_{A,B}}}{1} = L_1 + L_2 + L_3 + L_4 + L_5 - 2(M_{1,3} + M_{2,4} + M_{3,5}) + 2M_{1,5}$$

(2.12)

In general, the summation process is extended to as many segments as are contained in each of the individual elements. The larger the circuit, the more complex this becomes computationally.

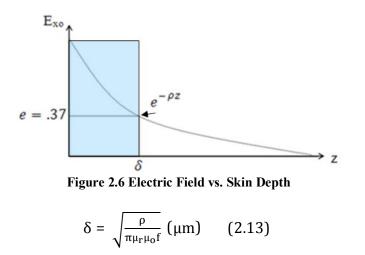

#### 2.3 Skin Effect

The phenomenon of the skin effect is well documented and is the tendency of current to flow on the surface or *skin* of a conductive material [21, 53]. In the case of a single cylindrical conductor, current flow is on the conductor's outer surface. For any given material, the depth of current flow, skin depth ( $\delta$ ), is determined by the relationship of current density (J) as a function of depth (*z*) within the conductor. The current density, as shown in Figure 2.6, is a decaying exponential function within a semi-infinite thick slab of material that has been excited by an incident electric field in the x-direction. As seen in this figure, the materials resistivity ( $\rho$ ) plays a roll by affecting the exponential

decay. The intersection of the point at which the magnitude of current density has been reduced to  $e^{-1} = .37$  is defined as the skin depth. Thus, materials with lower  $\rho$  will cause the exponential to decay faster and, as a result, force the current to flow closer to the conductor's surface as seen below in Equation (2.13).

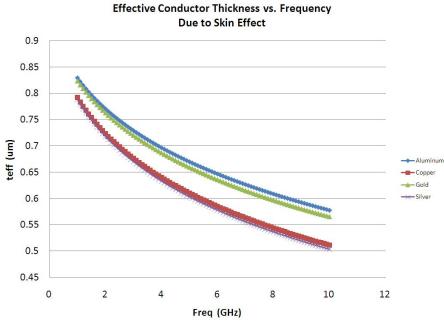

In semiconductor processing, trace resistance can be cast into terms of sheet resistance ( $R_{sheet}$ ) or ohms per square where length (L) and width (w) determine one square as seen in Equation (2.14) below.

$$R = \frac{\rho}{t} \frac{L}{w} = R_{sheet} \left(\frac{\Omega}{square}\right) \frac{L}{w} (square)$$

(2.14)

In the same way that metal thickness affects sheet resistance, the skin effect gives rise to a resistance ( $R_{skin}$ ) that affects the trace resistance in a similar manner by changing the effective thickenss of the conductor in which current can flow. In practical terms, a semi-infinite slab, while previously assumed, is not feasible. As such, effective thickness

must be determined as seen in Equation (2.15) by calculating  $\delta$  (Equation 2.13) and inserting the specific process parameter t for conductor thickness. In practice, the conductor current will not be limited or attenuated by the skin resistance if the metal thickness implemented is several skin depths thick. Inserting the effective thickness (t<sub>eff</sub>) into Equation (2.16) will produce a result of the true resistance of the conductor due to skin effect in ohms/square. One additional factor that affects R<sub>skin</sub> is the presense of current crowding at corners, which has the affect of decreasing the effective crosssectional area (t<sub>eff</sub>) of the conductor.

$$t_{eff} = \delta \left( 1 - e^{-\frac{t}{\delta}} \right) (\mu m) \qquad (2.15)$$

$$R_{skin} = \sqrt{\frac{\rho l}{W t_{eff}}} \left( \frac{\Omega}{\bullet} \right) \qquad (2.16)$$

Skin effect is an important aspect of inductor design because one of the techniques for improving inductor performance is to reduce conductor resistances by increasing trace widths and/or thicknesses [8]. In doing so, the traces are made less susceptible to undesired resistive parasitics from not being able to utilize the full conductor cross-sectional area [4].

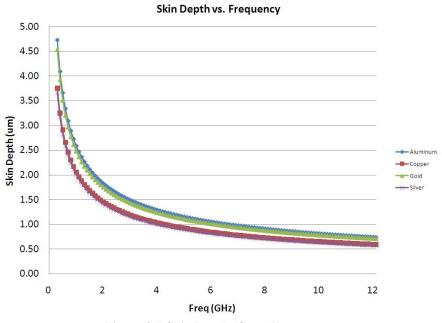

For common conductive materials like aluminum and copper, the skin depth at 1GHz is  $2.59\mu$ m and  $2.09\mu$ m, respectively. For quick estimates of skin depth, [9] provides a useful web-based tool. The plot seen in Figures 2.7 - 2.9 shows the impact of

frequency on skin depth, effective thickness, and resistance for various metals as previously discussed [4].

Figure 2.7 Skin Depth (δ) vs. Frequency

Figure 2.8 Effective Conductor Thickness (t<sub>eff</sub>) vs. Frequency

Figure 2.7 shows the relationship to the decrease in skin depth and effective conductor thickness with increasing frequency using Equations 2.13 and 2.15, respectively. Finally, Figure 2.9 graphically represents how the increase in resistance relates to frequency due to the  $\delta$  and t<sub>eff</sub> [4, 13]. In general, we can see that all metals exhibit a similar response; however, aluminum is affected slightly less than other materials. For this reason, many CMOS processes use aluminum for metallization.

#### CHAPTER 3 - MONOLITHIC CMOS PLANER INDUCTOR

This chapter will begin by discussing various monolithic CMOS planar inductor architectures. The electromagnetic fields present within a planar inductor will be presented as they apply to their respective inductor equivalent physical circuit model elements.

### **3.1 Inductor Architectures**

The monolithic CMOS planar inductor architecture has become widely used due to its relatively simple integration with existing CMOS capabilities and processing steps. The use of damascene processing and inter-layer vias has enabled integration of the inductor in the upper-most layers of standard multi-metal processes. This section will discuss the various planar inductor architectures being integrated in CMOS circuits. In a later chapter, the 3D inductor architecture of focus will be presented.

Figure 3.1a illustrates 4 common layout shapes found in modern inductive CMOS devices. The simplest geometry, or most commonly implemented, is the square spiral. The selection of this shape is a general result from limitations in CAD layout tools, which use simple polygons (also known as Manhattan design rules), rather than complex shapes. Subsequently, the shape selection results generally from expediency in layout rather than inductor function [23] and has the result of not necessarily producing the most efficient

designs. Research shows that circular shapes result in greater efficiency due to the reduction in current crowding within the device corners [21]. Figure 3.1b shows a circular planar inductor micrograph [11].

a) b) Figure 3.1 a) Planar Spiral Inductor Shapes [23] b) Circular Inductor [17]

Figure 3.2 shows, from left to right, the layout and cross-section in 2 directions for a typical 2-turn square inductor fabricated in a 2-metal process. Cross-section A-A' illustrates an inductor fabricated in the upper-most layer of metal (M2). Upper layers of metal are typically used to implement the inductor traces because they offer lower resistance since increased metal thicknesses are allowed [13]. Another advantage to device performance is a reduction in substrate coupling with the increased distance between the metal traces and the substrate. Cross-section B-B' illustrates the M1 underpass required to pass port 2 outside of the inductor traces for subsequent connection or termination. The underpass is usually made of the lowest possible metal in order to

decrease the inter-layer capacitance between the traces and underpass. Using a lower level of metal contributes to performance degradation and is reflected by a slight lowering of the self-resonant frequency ( $f_{sr}$ ).

Figure 3.2 Layout and Cross-Section of 2 Metal Square Spiral Inductor [21]

Note the use of the nomenclature  $D_{in}$  and  $D_{out}$  in Figure 3.2.  $D_{out}$  represents the outer-most dimension of the square inductor while  $D_{in}$  is the inner most. Another parameter,  $D_{avg}$ , will be referred to as the arithmetic mean of the previous two parameters. This convention is widely used when comparing the inductance values against an equivalent uniform current sheet. As shown in Equation 3.1, the ratio of the outer to inner diameters is referred to in literature as the fill factor ( $\rho$ ). This is intuitive by inspection since  $\rho$  approaches 1 when  $D_{out} \approx D_{in}$  and goes to 0 when it is becomes hollow [23].

Figure 3.3 illustrates a typical 3-metal architecture. This architecture is common when a large number of turns are needed to obtain the desired inductance value. This

technique is preferable as it reduces the series resistance by tying stacked layers of metal together. In this case, M2 and M3 are shorted mirror images as shown in cross-section A-A'. In this architecture, M1 is used for the underpass as seen in cross-section B-B'. The tradeoff is seen as an increase in interlayer capacitance [2, 3, 4, 44]

Figure 3.3 Cross-Section of Stacked and Shorted Spiral Inductor [21]

Figure 3.4 illustrates a final planar architecture. This architecture can be used to shield the electric field from termination in the substrate and is referred to in literature as a square planar spiral inductor with a patterned ground shield (PGS). Illustrated from left to right are the inductor layout followed by a pattern structure where a lower level of metal, most likely silicided poly silicon, is added just above the substrate. The PGS structure utilizes alternating N and P doped trenches placed orthogonally to the traces to oppose current flow by *shielding* the electric field from the substrate [1, 21]. This creates a high resistance return path to ground that acts to inhibit current flow in the substrate. The PGS as drawn shows a black "X", which is a metal 1 strap to ground. The ground strap provides the shortest path to ground if any current does flow. The third image is the

combination of the first two pictures using the PGS. The cross sections A-A' and B-B' show a three metal (M2, M3) shorted inductor with M1 being utilized to strap the polysilicon to ground in facilitating the underpass [1, 44].

Figure 3.4 Layout and Cross-Section of Spiral Inductor with PGS [1, 21]

In addition to the three common architectures presented, there have been many other methods researched and reported to address one or more parasitic issue. The interested reader can review [14] for a proton beam isolation method while [15] can be reviewed for deep trench isolation techniques.

## **3.2 Modeling the Planar Inductor**

Modeling inductor behavior has been a widely covered subject by many authors [12, 16, 17, 18, 22, 25, 44]; however, two primary modeling methods are used today: numerical methods, and the equivalent physical circuit model method. The numerical method is based upon finite element analysis (FEA) [4, 7, 16, 21]. This approach is based upon iterative convergence of the arithmetic mean distance and geometric mean distance of each wire segment with every other wire segment in the circuit. While accurate, this

method takes expensive software and a large amount of computing resources to complete even for small devices [17].

The planar equivalent circuit model derives its origin from the ability to completely understand all parasitic phenomena and related parameters present such that assignment of physical or simulated circuit components (resistors, capacitors, etc) are possible. This method allows for a reasonably accurate and faster model development at a reduced cost. Limitations of physical modeling can arise from undetermined highfrequency phenomena like eddy-currents [4, 16, 21]. However, developing an understanding of all parasitic factors allows for a more intuitive approach to modifying the inductor to achieve the desired design results. The physical model will be covered next.

# The Physical Model

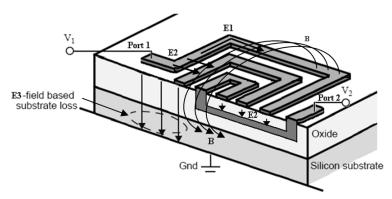

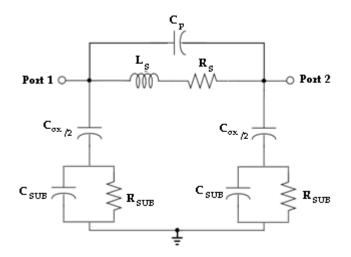

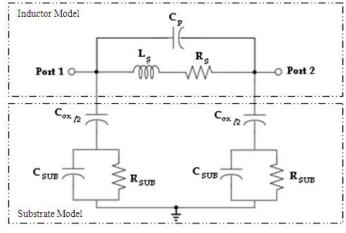

While topology choices for CMOS spiral inductors abound, the planar square spiral provides the best illustration of the electromagnetic fields exhibited and the utility of the physical model. As illustrated in Figure 3.5, one magnetic and three electric fields are produced when an AC voltage is applied [20]. The reader is referred to Figure 3.6 for the equivalent planar inductor circuit model.

The first electric field  $(E_1)$  is a result of the voltage difference between the terminal connections of the spiral and is simply due to ohmic losses in the traces [20].

This is directly dependent upon material resistivity ( $\rho$ ) and is modeled as the series resistance R<sub>S</sub>.

Figure 3.5 Electric and Magnetic Fields in a CMOS Planner Inductor [21]

The second electric field ( $E_2$ ) is a consequence of the voltage difference between any two turns in the spiral and any individual turn and the underpass [20]. This is a consequence of the second port being connected using a lower level of metal, which induces an inter-winding parasitic capacitance due to the presence of the interlayer dielectric. The modeling parameter for  $E_2$  is  $C_P$  [20].

The third electric field (E<sub>3</sub>) is present due to the voltage difference between the silicon substrate and the metal of the spirals. Field E<sub>3</sub> induces capacitive coupling to the substrate and is oftentimes the most predominant parasitic since it extends into the substrate [20]. This is modeled as the parameter C<sub>OX</sub>. The effect of this field is made worse because most CMOS circuits use low-resistivity substrates in the range of  $<10\Omega/cm$ . This allows for current to flow in the substrate easily. Due to this current

flow, it is necessary to include modeling parameters for the intrinsic substrate capacitance and resistance. These parameters are identified as  $C_{SUB}$  and  $R_{SUB}$ , respectively.

The final field is the magnetic field (B) produced by the AC current that flows through the traces of the spiral. While the magnetic field is what induces the desired inductive behavior, this also creates a complementary parasitic behavior in the metal traces due to eddy-currents as discussed in Chapter 2 [4, 20, 21, 24, 44].

Figure 3.6 Basic Planar Inductor Equivalent Circuit Physical Model [4, 20, 21, 24]

Further inspection of the physical model in Figure 3.6 shows the presence of two sub-models as seen in Figure 3.7. The first sub-model represents the inductor in free space and would be present for any inductor. The second is the model of any conducting metal placed on top of a silicon substrate.

Figure 3.7 Inductor Sub-Models [4, 20, 21, 24]

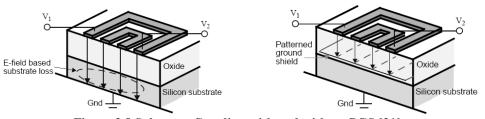

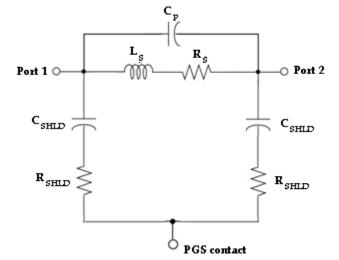

As previously shown in Figure 3.4, the planar inductor architecture was modified to include a patterned ground shield that acts to shield the field E3 prior to it penetrating into the substrate [1, 2, 20, 21]. Figure 3.8 shows graphically side-by-side the comparison between the two methods while Figure 3.9 illustrates the addition of the ground shield in the equivalent physical circuit model. The corresponding model element changes involve removing  $C_{OX/2}$  and replacing  $C_{Si} \parallel R_{Si}$  with series elements  $C_{shld}$  and  $R_{shld}$ . This modification is commonly implemented to achieve higher device performance.

Figure 3.8 Substrate Coupling with and without PGS [21]

Figure 3.9 Basic Planar Inductor Equivalent Circuit Physical Model with PGS [21]

Reflecting on Figures 3.5 and 3.6, it becomes more intuitive of how to optimize device performance. The first parameter,  $R_s$ , can be reduced by utilizing low resistivity materials like copper or aluminum for metallization. Another method would be to tie two or more exact image metal layers together as illustrated in Figures 3.3 and 3.4; however, an increase in  $C_{ox}$  will be traded for the reduction in resistance as a result of the M1-M2 capacitance adding to the M1 to substrate MOS capacitance. The oxide capacitance can be reduced by increasing the inter-layer dielectric between the M1-M2 layers, by increasing the height that the inductor is placed above the substrate, or by adding a PGS [1, 15, 16, 18, 19, 21].

Next, the line trace-width to space-ratio of the traces should be as wide as possible until the sidewall capacitance  $C_{sw}$  increases with a tradeoff of decreased self-

resonant frequency. A few suggestions to reduce the feed-thru capacitance would be to increase the space between the turns and the underpass, eliminate the underpass completely, or keep the device footprint as small as possible. Elimination of the underpass in the planar architecture is not feasible without using the center tap as a bond pad, which would introduce additional parasitics. Feed-thru capacitance degrades the self-resonant frequency, thus any improvements to this parameter will help to minimize existing degradation.

A reduction in  $C_{OX}$  can be achieved by increasing the oxide thickness resulting in the inductor setting higher above the substrate. One final technique would be to increase the substrate resistivity. This, however, can make it difficult to integrate with other CMOS devices where speed and cost are factors.

# CHAPTER 4 – PARAMETER CALCULATION METHODS

This chapter will briefly review the calculation methods for the modeling parameters identified in Chapter 3. Coverage of inductance will cover the most widely accepted method, which is the Greenhouse Method [11]. This chapter will include coverage for both the calculation and plot extraction methods needed to determine the key performance metrics related to inductor evaluation. Additionally, coverage of the quality factor (Q), and self-resonant frequency ( $f_{SR}$ ) will be discussed.

#### 4.1 Inductance (L) Calculation

As discussed in Chapter 2, inductance is the measure of a coil's ability to store magnetic energy within its windings and is based primarily on the magnetic flux density created from the current density. Many varying analytical formulas for calculating inductance exist in literature with some being more accurate than others. Within these formulas, it is often unclear what restrictions or boundary conditions apply to them [23]. With so many formulas available, only the Greenhouse Method will be discussed. The interested reader can review [5, 7] for a historical progression of the art of inductance calculation methods.

#### Greenhouse Method

In the case of non-standard geometric shapes, most designers utilize numerical techniques, curve fitting, and empirical formulas as reported in [7]. A couple of the numerical techniques utilized here are cross-sectional area integration, Taylor series expansion, and geometric mean distance. With the proliferation of silicon-based CMOS devices, Greenhouse furthered the art by developing an algorithm-based approach motivated from Grover's methods by calculating inductance as the summation of all mutual- and self-inductances of individual line segments [7]. In the case of orthogonal line segments, only a weak mutual coupling exists and thus is not considered. Basic calculations for mutual- and self-inductance were shown in Chapter 2.

Extending the Greenhouse algorithm to the case of Figure 4.1, the mutual- and self-inductance can be calculated by breaking the inductor into individual line segments. The total inductance ( $L_{Total}$ ) of the inductor with five line segments is then calculated by extending Equation (2.5), where  $L_i$  represents the self-inductance of each line segment "i", and  $M_{i,j}$  is the mutual-inductance between the two line segments "i" and "j".

Equation (4.1) is obtained by taking the self-inductance of each line segment, then adding the mutual-inductance for each parallel line segment pair that has current flow in the same direction, and subtracting the mutual-inductance for each parallel line segment pair that has current flowing in the opposite direction.

Figure 4.1 Greenhouse Method [7, 11]

$$L_{\text{Total}} = L_1 + L_2 + L_3 + L_4 + L_5 - 2(M_{1,3} + M_{2,4} + M_{3,5}) + 2M_{1,5}$$

(4.1)

The above approach relies on Equations (4.2)-(4.6) reported by Greenhouse in [11] for calculating either the self- or mutual-inductance of each line segment. This relies on geometric factors:

- Conductor Width (w) in microns

- Conductor Thickness (t) in microns

- Distance Between Conductor Filaments (d)

- Relative Permeability (µ)

- Geometric Mean Distance (GMD)

- Arithmetic Mean Distance (AMD)

- Mutual Inductance Parameter (Q)

- Frequency Correction Factor (T)

$$L_{i} = 0.0002 \cdot l_{i} \left( ln \left( 2 \cdot \frac{l_{i}}{GMD} \right) - 1.25 + \frac{AMD}{l_{i}} + \mu \cdot \left( \frac{T}{4} \right) \right) \quad (4.2)$$

$$M_{i,j} = 0.0002 \cdot l_{i} \cdot Q_{i} \quad (4.3)$$

$$ln(GMD_{i}) = ln(d) - \frac{1}{12 \cdot \left( \frac{d}{w} \right)^{2}} - \frac{1}{60 \cdot \left( \frac{d}{w} \right)^{4}} - \frac{1}{168 \cdot \left( \frac{d}{w} \right)^{6}} - \frac{1}{360 \cdot \left( \frac{d}{w} \right)^{8}} \dots \quad (4.4)$$

$$Q_{i} = ln \left( \frac{l_{i}}{GMD} + \left[ 1 + \left( \frac{l_{i}}{GMD} \right)^{2} \right]^{0.5} \right) - \left[ 1 + \left( \frac{l_{i}}{GMD} \right)^{2} \right]^{0.5} + \frac{GMD}{l_{i}} \quad (4.5)$$

$$AMD = w + t \qquad (4.6)$$

# Revised Greenhouse Method

The above Greenhouse algorithm applies to the ideal case of a rectangular inductor in free space. In [24], Krafcsik and Dawson later revised the Greenhouse algorithm by accounting for the non-free space ground plane exhibited in CMOS devices as shown in Figure 4.2. This research brought to light the presence of a reflected image in the substrate below the ground plane interface at a distance equal to the distance the inductor sits above the ground plane. Unfortunately, this image acts to reduce overall inductance by contributing a negative mutual-inductance (negative current), as presented in Equation (4.7).

Figure 4.2 Reflected Image [24, 5]

$$L_{\text{Total,CMOS}} = \left[ L_1 + L_2 + L_3 + L_4 + L_5 - 2(M_{1,3} + M_{2,4} + M_{3,5}) + 2M_{1,5} - M_{1,1'} + M_{2,2'} + M_{3,3'} + M_{4,4'} + M_{5,5'} + M_{1',5'} \right]$$

(4.7)

When more accurate results are required, the use of full magnetic wave field solvers can be used. This can be the case when implementing non-standard geometric shapes or when highly complex line segment structures are being used. However, the major drawback of this method is the length of simulation time, often taking days, and the cost of related systems and software.

## 4.2 Series Resistance (R<sub>s</sub>) Calculation

At low frequencies, below ~500MHz, series resistance can be approximated by measuring the simple DC resistance or using the derived  $\text{Re}[Z_{11}]$  value from the 1-Port  $S_{11}$  measurement as shown in [49]. As operational frequencies have increased above 500MHz, it was observed that the accuracy of the model started to deviate from expectations as it didn't remain constant. Several authors have investigated this and have identified the presence of a frequency dependent component. This dependence is understood to be a result of contributions from both the presence of skin depth and eddy-currents. As such, Yue and Wong. and Yue, et al. reported in [16, 25] that a good closed form approximation is shown in (4.9), where the following parameters are defined:

- *l* is the spiral length

- $\rho$  is the resistivity at DC

- $\delta$  is the skin depth of the metal

- t is the metal trace thickness

- w is the metal trace width

$$R_{S} = \frac{\rho l}{W t_{eff}} = \frac{\rho l}{W \delta(1 - e^{\frac{-t}{\delta}})}$$

(4.8)

Equation (4.8) show the series resistance is frequency dependent upon the skin effect previously shown in Equation (2.6), the length, width, and thickness of the inductor wire trace. The series resistance can be determined from measured 1-port values by converting the S-parameter  $S_{11}$  to  $Z_{11}$  and taking the real part of the complex impedance.

# 4.3 Feed-Thru Capacitance (C<sub>P</sub>) Calculation

The feed-thru capacitance value  $C_p$  takes into account the contribution from two parallel plate capacitances. The first is the capacitance created between the sidewall area and inter-winding distance ( $C_{sw}$ ) (4.9), while the second is the capacitance due to the underpass (m1) and the inductors M2 traces ( $C_{up}$ ) (4.10) [16]. The combined equation is shown in (4.11). Due to the small contribution from the sidewall capacitance, a good approximation for  $C_p$  is  $C_{up}$  as shown in (4.12).

- d is the horizontal distance between traces (i.e., Space length)

- 1 is the length of the inductor

- t is the metal thickness

- n is the number of turns over the underpass

- w is the line width

- $\varepsilon_0$  is the permittivity in a vacuum

- $\epsilon_r$  is the relative permittivity

$$C_{sw} = \frac{(\varepsilon_0 * \varepsilon_r) \cdot l \cdot t}{d} = \frac{\varepsilon_{ox} \cdot A_{sw}}{d} \qquad (4.9)$$

$$C_P = \mathbf{n} \cdot \mathbf{w}^2 \cdot \frac{\varepsilon_{ox}}{t_{ox,M1-M2}}$$

(4.10)

$$C_P = C_{sw} + C_{up}$$

(4.11)

$C_P \approx C_{up}$  (4.12)

#### 4.4 Oxide Capacitance (Cox) Calculation

The oxide capacitance parameter represents the parallel plate capacitance created by the inductors metal traces above the silicon substrate with the  $SiO_2$  dielectric layer sandwiched in between. The oxide capacitance is a straight forward calculation from parameters as shown in (4.13).

$$C_{ox} = \frac{(\varepsilon_o * \varepsilon_r) \cdot A}{t_{ox}} = \frac{\varepsilon_{ox} \cdot A}{t_{ox}}$$

(4.13)

## 4.5 Silicon Resistance (R<sub>si</sub>) and Capacitance (C<sub>si</sub>)

The semiconductor substrate layer resistance and capacitance are represented by the parasitic parameters  $R_{si}$  (4.14) and  $C_{si}$  (4.15), respectively. In these two equations, the additional parameters  $C_{sub}$  and  $G_{sub}$  are present. The additional parameters represent the capacitance and conductance per unit area, respectively, and can be obtained from measured data. Substrate resistance  $R_{si}$  is predominantly determined by the majority carrier concentration as determined by doping concentrations and the area the inductor occupies [12]. The substrate capacitance is the self-capacitance and is attributed to the high frequency effects occurring in the substrate [18, 25]. Additionally,  $R_{si}$  and  $C_{si}$  can be approximated as being proportional to area.

$$C_{si} = \frac{1}{2} \cdot l \cdot w \cdot C_{SUB} \quad (4.14)$$

$$R_{si} = \frac{2}{l \cdot w \cdot G_{SUB}} \quad (4.15)$$

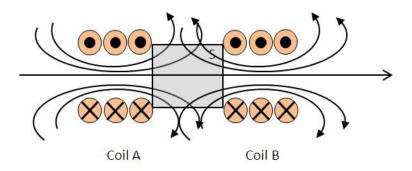

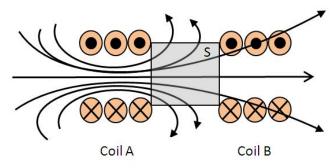

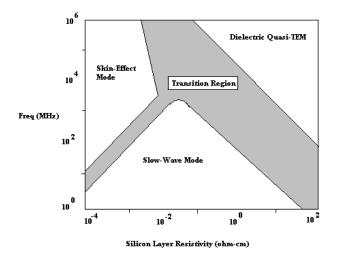

In [26], Hasegawa et al. illustrates the presence of three distinct modes of operation that affect the silicon layer resistivity with a microstrip line situated above on an SiO<sub>2</sub> layer. The three modes of operation are Dielectric Quasi-TEM Mode (DQTM), Skin-Effect Mode (SEM), and Slow-Wave Mode (SWM). These modes are a result of the electric and magnetic fields generated from the AC signal. The properties are thus a function of electric permittivity and magnetic permeability.

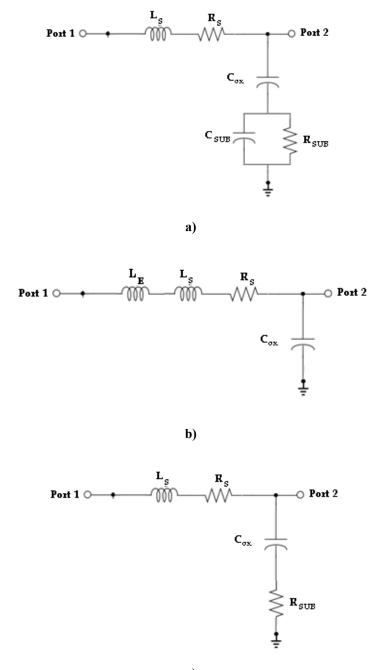

In the mode DQTM, both the frequency and substrate resistivity are typically high. In this mode, almost all of the energy is transmitted through the silicon layer as a displacement current. This is illustrated in the circuit model as shown in Figure 4.3a. In SEM, the substrate acts as a lossy conductor as illustrated in Figure 4.3b. This occurs when the quantity of the frequency and the conductivity is large. The final mode, SWM, occurs when a moderately doped substrate (<1 Ohm-cm) and frequency is being used. This mode is illustrated in Figure 4.3c. This third mode was typical of CMOS circuits until operating frequencies were raised above 500MHz. Other literature refers to this as the Quasi-Static TEM [26]. Between the three modes lays a distinct transition region as illustrated in Figure 4.4, regenerated from [26] where dual modes might be present. DQTM is the most practical mode as frequencies reach into the GHz range.

c) Figure 4.3 Modes of Operation Circuit Diagrams [26]

Figure 4.4 Modes of Operation [26]

# 4.6 Quality Factor (Q) Calculation

The quality factor (Q) is another critical parametric that abounds in formulas that have been adjusted depending on geometry, etc. However, the true meaning of Q is simply the efficiency of an inductor to store energy in spite of parasitic effects. The fundamental definition is thus based upon the energy Equation (4.15) and is a dimensionless parameter [1, 13, 25, 43].

$$Q = 2\pi \frac{|\text{Peak Magnetic Energy}-\text{Peak Electric Energy}|}{\text{Energy Loss in One Oscillation Cycle}}$$

(4.15)

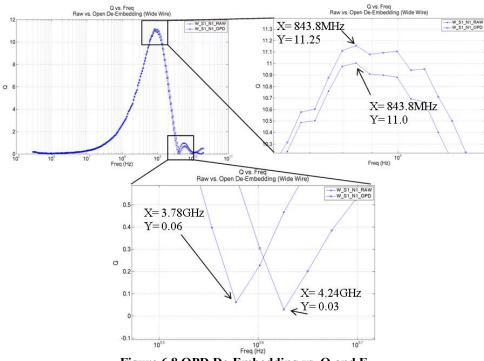

A quality factor estimate for an ideal inductor can be achieved by plotting Equation (4.16). A good approximation to this can be obtained from the complex impedance  $Z_{11}$  from a 1-port S-parameter measurement where  $\omega \cdot L_S$  represents the reactive part and  $R_s$  the real part [1, 13, 25, 43].

$$Q = \frac{\omega \cdot L_S}{R_S} \approx \frac{|X_L|}{R_S} = \frac{Imag(Z_{11})}{Real(Z_{11})}$$

(4.16)

Equation (4.16) above is an approximation and does not fully account for all of the parasitic affects present when designing inductors over Si-SiO<sub>2</sub>. As such, two additional terms need to be added to Equation (4.17) [13, 25, 43]. The first is the substrate loss factor, which accounts for the energy that is dissipated in the substrate. The second is the self-resonance factor, which accounts for both Q peaking and other reductions as discussed in the next section. As such, Equation (4.17) presents the silicon based quality factor in terms of variables discussed previously in this chapter.

$$Q = \frac{\omega \cdot L_{S}}{R_{S}} \cdot \frac{R_{Si}}{R_{Si} + \left[\left(\frac{\omega L_{S}}{R_{S}}\right)^{2} + l\right] \cdot R_{S}} \cdot \left(1 - \frac{R_{Si}^{2} \cdot \left(\frac{C_{OX} \cdot C_{Si}}{C_{OX} \cdot +} + C_{S}\right)}{L_{S}} - \omega^{2} L_{S} \left(\frac{C_{OX} \cdot C_{Si}}{C_{OX} \cdot +} + C_{S}\right)\right)$$

(4.17)

Substrate Loss Factor

Substrate Self-Resonace Factor

One additional method commonly used in HF designs is shown below in Equation (4.18). This results from plotting of power transfer function  $|Hj\omega|$  in decibels (db). Here the center frequency  $\omega_0$  is found at the power transfer function peak and  $\Delta\omega$  (also called

the band width BW) is found at the -3db power point where the differences between the upper and lower values of  $\omega$  are extrapolated.

$$Q = 2\pi \frac{\omega_o}{\Delta \omega}$$

(4.18)

# 4.7 Self-Resonant Frequency (f<sub>SR</sub>) Extraction

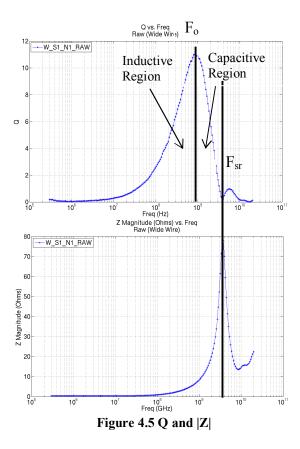

The first self-resonant frequency  $(f_{sr})$  is a critical inductor parametric. This parameter represents the first frequency at which the impedance of the inductor and the capacitor are equal in value and are thus caused to resonate. This is referred to in literature as self-resonance. Figure 4.5 shows typical Q and |Z| versus frequency inductor plots that has been stacked. Careful observation shows that from DC up to the characteristic frequency ( $f_o$ ), the plot of the quality factor is inductance whereas from  $f_o$ to  $f_{sr}$  it is capacitive. In the bottom plot, it also becomes evident that  $f_{sr}$  can be determined by the peak of |Z|.

Knowing the self-resonance frequency, the capacitance at the self-resonant frequency can also be determined by Equation (4.17 and 4.18) [1].

$$f_{\rm sr} = \frac{1}{2\pi\sqrt{L_{\rm sr}.C_{\rm sr}}} \tag{4.17}$$

$$C_{\rm sr} = \frac{1}{(2\pi f_{\rm sr})^2 \cdot L_{\rm sr}}$$

(4.18)

#### **CHAPTER 5 - 3D INDUCTOR**

This chapter will introduce the underlying 3D inductor architecture and briefly cover the unique manufacturing process. For a detailed understanding of the necessary design cycles needed to obtain and optimize a device for manufacturing, [28-34, 36] can be reviewed for further understanding. Additionally, new design parameters will be introduced.

# 5.1 Architecture

Device designers have sought to improve inductor performance by pursuing 3D architectures that utilize the area above the wafer surface. In most cases, the devices have one side abutted to the silicon surface while others have attempted to use micro-machining techniques to suspend the inductor in some fashion. Unfortunately, most of these variations have tradeoffs in either manufacturability or mechanical instability that make them less preferable for implementation within a CMOS process.

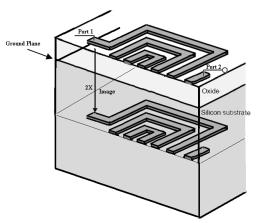

The 3D inductor presented here, using through-wafer interconnect vias, offers a unique approach by using both the top and bottom wafer surfaces for patterning the metal traces. This technology relies on the ability to implement high aspect ratio TWVs for connecting the top and bottom surfaces of the wafer. Thus, a 1-turn inductor has a single trace on each the top and bottom wafer surface connected by two vias. This approach is

similar to planar technology that ties multiple stacked metal layers together with interlayer vias. In this case, however, rather than a 1um long via through inter-layer dielectric (ILD), the via spans the thickness of the wafer (~500um). The overall inductor length is only limited by the via processing technology and final desired wafer thickness.

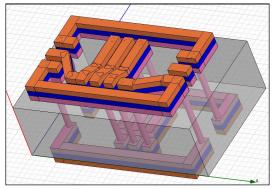

Figure 5.1 shows a 3D physical model of a 3-turn inductor using Ansoft's HFSS 3D full-wave electromagnetic field simulation layout tool. The material layers have been thickened here to better emphasize the individual layers present. The grey translucent box represents the silicon wafer. Orange is metall (M1) copper while blue is the TiN seed layer and pink is a diffusion barrier layer of parylene. As illustrated here, the inductor was laid out for 1-port ground-signal-ground (GSG) RF testing. Port 1 is shown at the left-center contact while port 2 is attached to the guard ring on the lower right contact. Notice that the guard ring is present on both the top and bottom surfaces of the wafer and is connected by TWVs. The guard ring provides isolation from extrinsic noise while taking measurements.

Figure 5.1 HFSS 3D Inductor Architecture

The 3D TWV design topology offers some advantages when compared to traditional planar spiral inductors. The largest of which is found in exploiting the silicon substrate. Figure 5.2 illustrates the area savings that can be realized for a 3-turn equal line-space 3D inductor. As shown, it's possible to obtain a 40% similar area device with a tradeoff in a full thickness wafer being used and thus creating a 36 times longer inductor. When a larger 3D inductor is desired, the area impact results in a 40% area increase and a 30% length increase per turn. The same 1-turn increase on a conventional planar device results in both an area and length increase of 40%.

A unique advantage of the 3D inductor occurs as a result of using the TWV technology. The inductor length can be tuned in production without adjusting the layout that would otherwise have resulted in additional costs associated with spinning new reticles. This becomes apparent with realization that the backside grind process step allows for customized control of the inductor length. Additionally, the underpass is no longer needed and will eliminate the underpass coupling.

# 5.2 3D Inductor Fabrication

As with fabricating any new device, integration is limited by the ability of additional processing steps and techniques to be compatible with the existing CMOS process flow. The dominant CMOS processing steps rely heavily upon wet and dry etching techniques. Recent advances in both wet and dry etching techniques have made the realization of the 3D inductor using TWVs possible. While both wet and dry etching technologies have been able to create vias for decades, the advancements in plasma-based dry etching techniques have only recently allowed formation of the high aspect ratio TWV in a production environment possible. New chemistries now offer the ability for a highly selective process over a wide range of materials [27]. The 3D TWV inductor is now well suited for CMOS integration.

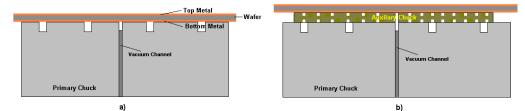

While most CMOS processes limit the amount of backside processing, this topology exploits the ability to use both wafer surfaces. As a result, processing steps

44

need to account for this with additional masks and must take measures that will afford appropriate reverse side surface protection. This will become more apparent in the device measurement chapter as it will be necessary to account for the traces on the reverse side of the wafer.

## The Process Flow

The following process flow was developed in collaboration between Boise State University (BSU) and MCNC Research Development Institute under U.S. Government research contract N66001-01-C-8034 to develop TWV technology. The manufacturing process flow that follows is based upon this work. As such, the flow will only outline the basic concept of via formation and subsequent transformation into the 3D inductor. Not all details related to fabricating the via will be covered. The inductors were fabricated in the MCNC .3um process.

#### The Original 3D Inductor Mask Set

A 3D inductor mask set was created (Figure 5.3) that used polygon lines to pattern the inductor wire traces. It was discovered while processing the first couple of wafers that Dupont's WB5030 dry film photoresist did not have the optical resolution to adequately resolve the line width spacing without creating shorts between adjacent traces [36]. As such, a design rule was needed to set the minimum line-to-line spacing to 30um. The original mask set used 16um spacing. The reticle masks and poor results produced by this reticle set are illustrated in Figure 5.3.

# The New 3D Inductor Mask Set

A second set of masks were created to ensure a minimum 30um line-to-line spacing design rule was implemented. Additionally, the new mask set focused on using straight-lined traces that were off-angle. Two types of inductors were developed for measurement. The first type will be referred to as the wide trace (WT) width vs. narrow space and the other will be a narrow trace (NT) width vs. a wide space as shown in Figure 5.4d-e. The drawn line widths are WT = 70um and NT = 25um while the spaces are 30um and 100um, respectively

Figure 5.4a-c identify the masking levels where a) shows the via mask, b) shows the top metal mask with ground-signal-ground (GSG) probe pads and guard ring, and c) shows the bottom metal mask with guard ring. Figure 5.4d-e shows all masks overlaid to make up the wide and narrow trace inductors.

#### TWV Etching

The via formation is the enabling technology for realization of the 3D TWV inductor. In most CMOS processes, the TWV would be started in the front end of the line; however, this could be tailored as dictated by the process.

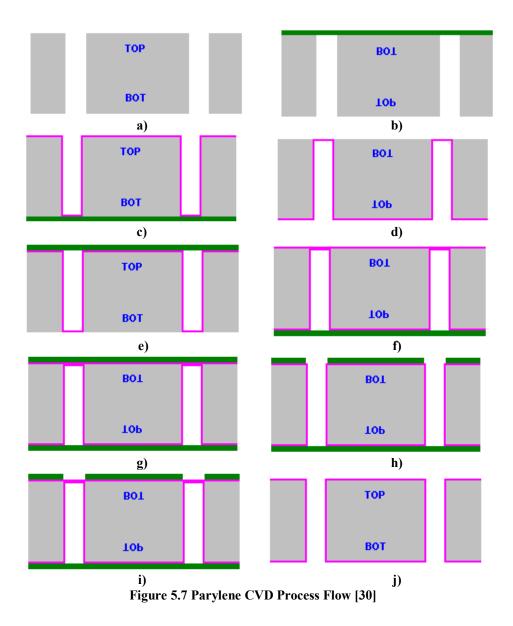

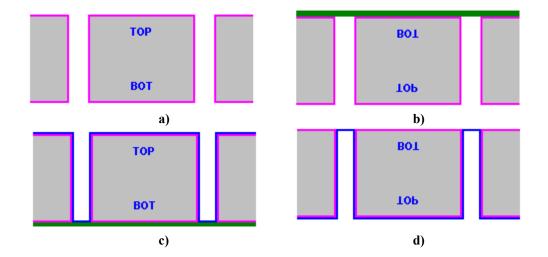

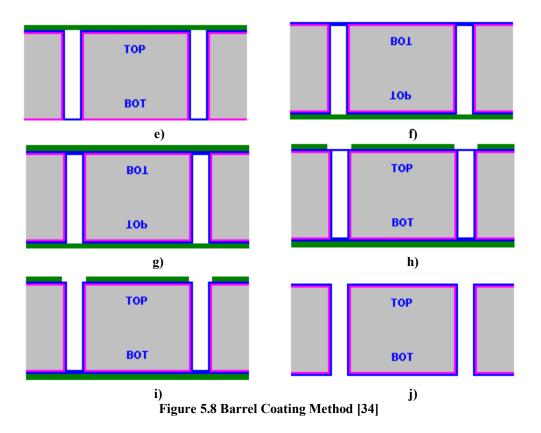

Figure 5.5a-g shows the processing steps required to form the TWV. The process begins with a bare 500um wafer as shown in a). In b), a thermal oxide is grown to provide an etch stop on the backside of the wafer. A thick layer of positive develop photo resist is also deposited on the wafer backside to provide protection while in the Oxford Instruments Plasmalab Model 100 using a licensed deep reactive ion (DRI) Bosch etch process [29]. A thick layer of the same resist is then spun on the top side of the wafer c) to receive the TWV photo mask pattern. The TWV pattern is then transferred onto the wafer using a contact aligner followed by exposure and bake. The wafer is then placed in a wet developer to activate the photo resist followed by a strip and cleaning with a deionized rinse. In d), the wafer is put in the Bosch DRI tool and the via is etched using a chemistry of  $SF_6$ . The via is formed by subjecting the pattern to a predetermined number of iterative anisotropic etch and passivation steps ( $\sim$ 500) [29]. This allows for the silicon to be removed in the vertical direction while the sidewalls stay protected. Once the oxide etch stop has been reached on the backside of the wafer, the top and bottom side resists are stripped. The TWV is etched with an aspect ratio of 10:1. The final step in the via hole formation is to remove the oxide on the backside of the wafer.

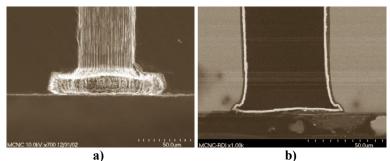

It was observed during the final etch steps prior to punching through that degradation occurred in the via profile at the bottom of the via. The via profile was suspiciously wider. It was discovered that by using the thermal oxide as an etch stop on the backside of the wafer, excess charge buildup occurred. This resulted in a breakdown of the sidewall passivation and thus the silicon was etched in the horizontal direction. It was also noted that not all vias etched at the same rate. As such, vias that etched faster thus continued the etching through the oxide and continued to etch into the thermal chuck. Figure 5.4a shows a scanning electron microscope (SEM) micrograph depicting the results of the oxide charge buildup on the via profile [30].

Two methods were used to mitigate this issue and provide a more robust process. The first was to reduce the RF power source. Figure 5.6b shows the corresponding improvement in the via profile. The second method was to use a sacrificial carrier wafer affixed to the bottom side of the target wafer. Affixing the carrier wafer to the target wafer occurred by using photo resist as an adhesive bonding layer.

Figure 5.6 Via Profile with Oxide Charge Buildup [30]

# Conformal Insulator Barrier Deposition

Copper was selected to be the metal of choice to fill the vias and pattern the inductor traces due to its lower resistivity than aluminum. With the use of copper, it becomes necessary to provide a diffusion barrier layer that prohibits the copper from

migrating into the silicon. If not inhibited, deterioration of interconnects or deep-level traps in the silicon that could lead to increased standby leakage [31].