# Boise State University **ScholarWorks**

Electrical and Computer Engineering Faculty Publications and Presentations

Department of Electrical and Computer Engineering

4-1-2005

## Novel Slurry Solutions for Thick Cu CMP

Peter A. Miranda Boise State University

Jerome A. Imonigie *Boise State University*

Aaron L. Erbe Boise State University

Amy J. Moll Boise State University

This document was originally published by IEEE in *IEEE Workshop on Microelectronics and Electron Devices, 2005.* Copyright restrictions may apply. DOI: 10.1109/WMED.2005.1431630

### Novel Slurry Solutions for Thick Cu CMP

Peter A. Miranda, Jerome A. Imonigie, Aaron L. Erbe, Amy J. Moll

Department of Materials Science and Engineering

Boise State University

Boise, ID

Abstract—Electro-plating methods currently used to deposit Cu in through-wafer interconnect applications result in the formation of a thick Cu layer with large amounts of topographical variation. In this paper, alternative methods for thick Cu removal are investigated using a two-step slurry CMP approach.

#### I. INTRODUCTION

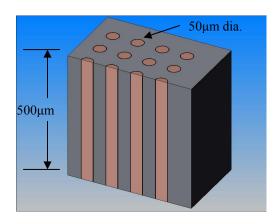

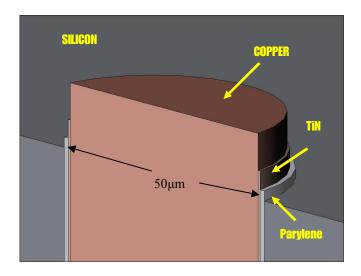

Three dimensional (3D) die stacking has become a viable source of solving next generation packaging needs for higher functioning integrated circuits. One novel configuration of chip stacking incorporates the use of copper through-wafer interconnects (TWI's) to provide electrical connectivity between stacked layers of silicon die. Interconnects are formed by a series of processing steps which parallel many of the conventional methods used in IC fabrication. First, small holes, or vias, are patterned across the wafer using photolithography. The vias are then created in the wafer by deep reactive ion etching. Secondly, a parylene insulator film is deposited to provide electrical isolation between the vias followed by the deposition of a diffusion barrier to protect against Cu diffusion into the silicon. Finally, an electroplated Cu layer is deposited on top of a Cu seed film, consequently filling the vias. After Cu deposition, CMP is used to remove the excess Cu leaving the Cu inside the vias intact. The vias are then tested for functionality using electrical characterization methods. A 3D solid model of cross-sectioned wafer with TWI is shown in Figure 1. Figure 2 is a cut-away picture showing the different layers formed as a result of the TWI process.

Figure 1. Cross sectional solid model of TWI.

Figure 2. Solid model cut-away view of a single TWI showing the different layers formed by deposition.

#### A. Thick Electroplated Cu

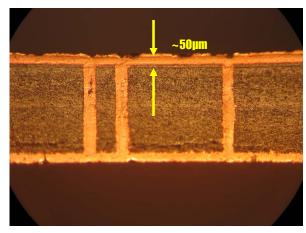

Two plating methods have been pursued in an attempt to deposit the Cu uniformly while minimizing the final Cu thickness. In work done by Burkett et al. [1], a patterned mask was used to permit Cu deposition only in designated areas where vias were present. Although this type of plating scheme did minimize the amount of Cu deposited on the surface of the wafer, problems were encountered during CMP processing associated with vacuum pick-up/transfer of the wafer due to the patterned "bumps". The plating methods used currently result in the deposition of Cu across the entire wafer starting inside of the vias, progressing outward toward the surface of the wafer until the entire surface of the wafer is covered. This "bottomup" via fill method results in a large amount of Cu being deposited on both sides of the wafer. With as much as 50µm of Cu deposited on each side, plating uniformity becomes difficult, consequently producing layer thickness variation with levels reaching 25%. Figure 3 is a picture of a completed wafer after the electroplating process.

Figure 3. Cross-section view of TWI showing the extreme Cu thickness and non-uniformity across the top and bottom surface of the wafer after the electroplating process.

#### B. CMP Challenges

In typical IC fabrication processes, chemical mechanical planarization (CMP) is the process used to remove topographical variation of metals or oxide layers on the surface With next generation integrated circuits of the wafer. incorporating more levels for increased functionality, CMP has become a critical step in allowing multi-level structures to become realized. However, conventional techniques used in Cu CMP involve layer thicknesses in the 0.5µm to 2.0µm range, much thinner than those used in TWI applications. CMP slurries currently available to industry for Cu applications are primarily designed for much thinner metal layers such as those used in dual damascene architecture. Based on in-house preliminary testing results, off-the-shelf slurries do not provide the mechanisms needed to successfully remove thick Cu using a one-step process recipe. Although selected slurries did provide improvements to within-wafer-nonuniformity (WIWNU) during CMP because of inherent lower removal rates, they did not warrant their use due to excessive slurry consumption that would be required to remove thick Cu layers.

Experimental aggressive slurries did provide higher removal rates such as those experienced in work done by Qiao et al. [2], however, using a one-step aggressive slurry would result in nonuniform Cu removal exposing isolated areas of the wafer consequently leading to excessive dishing and erosion of TWIs.

One approach to solving thick Cu removal scenarios incorporates the use of a two-step method for Cu removal. An aggressive slurry is initially used to remove the bulk Cu followed by a second, less aggressive slurry to complete the removal process. By using two types of slurries, an aggressive slurry could be used initially to remove the bulk Cu followed by a more mild slurry to remove the remaining Cu minimizing the possibility of dishing and erosion of TWIs. In a study performed by Peterson et al. [3], a two-step slurry CMP approach was presented as an alternative method for Cu CMP, however, the thickness of Cu was much thinner than that typically used in TWI applications.

#### II. EXPERIMENTAL METHODS

To test the two step process, a study was performed investigating the application of using two types of slurries to remove thick layers of electro-plated Cu. Two different types of slurries from Fujimi Corp. were chosen to be used in the study. Both slurries used in the experiments contained colloidal silica as the abrasive particle system with slightly different operating pH levels. An experimental slurry specifically designed for aggressive Cu removal was used as the first-step with the second slurry consisting of a common off-the-shelf slurry used in industry for mild Cu removal requirements.

To begin, 4L of the experimental slurry was prepared with 30% hydrogen peroxide ( $H_2O_2$ ) added at the point of use for a final  $H_2O_2$  concentration of 1.5%. The experimental slurry had a mean abrasive particle size of 30nm and a pH of 9.2. A four-inch diameter wafer was used in the experiment with a starting Cu thickness and nonuniformity of 50µm and 25%, respectively. The CMP tool used in the study was a Strasbaugh 6DS-SP Planarizer with the following machine parameters set during the process:

Down Force: 69kPaSpindle Speed: 100rpm

• Table Speed: 100rpm

• Slurry Flow Rate: 100ml/min

The type of pad used in the study was a Thomas West Industries 711 pad with an X-Y pattern and conditioning was performed prior to and in between runs. During the aggressive Cu removal stage, the wafer was inspected and measured for Cu thickness at 60sec intervals to avoid overpolishing. After an average Cu thickness of  $8\mu m$  was obtained across the wafer, the second-step slurry was introduced.

For the second-step slurry, 4L of Fujimi Planarlite 7102 slurry was prepared which also contained colloidal silica as the abrasive particle type with a mean particle size of 35nm and a pH of 6.1. As with the first slurry, hydrogen peroxide was added at the point of use for a final concentration of 1.5%. Again, the Thomas West 711 pad was used with multiple conditioning routines performed between slurry usages to minimize any cross contamination between slurries. The machine parameters were also changed to accommodate the less aggressive nature of the second-step slurry and were as follows:

• Down force: 41kPa

• Spindle Speed: 60rpm

Table Speed: 60rpm

• Slurry Flow Rate: 100ml/min.

#### III. RESULTS

During the aggressive Cu removal stage, an average removal rate of  $10\mu m/min$  was achieved. Because of the high removal rates experienced during the first-step process, nonuniformity of the Cu surface increased during CMP and

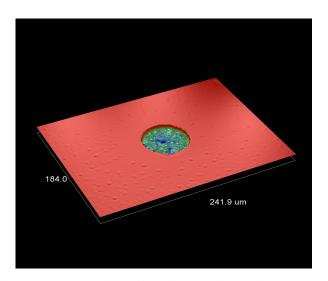

resulted in the WIWNU to be ~20% with an average Cu thickness of 8-10µm. Nonuniform Cu removal was also compounded by the plating variation present on both sides of the wafer prior to CMP. Both sides of the wafer were processed using the first-step slurry for approximately 3-4 minutes at 1 minute intervals. With the second-step slurry, additional run time was required to complete the removal process due to the much lower removal rate of  $1.0\mu m/min$ . During the second-step slurry process, small improvements in nonuniformity were made due to the slower removal rate. Figure 4 shows an optically scanned image of an isolated via taken after completion of the two-step process method. Figure 5 is the same via taken with a high powered microscope. Some dishing of the vias was observed during CMP as a result of nonuniform Cu removal.

#### IV. CONCLUSIONS

In conclusion, slurries currently available for Cu CMP are not designed for thick Cu and warrant new methods to be developed for thick Cu applications. Although a two-step slurry method does appear to be a viable solution for thick Cu removal, care must be taken to avoid issues with excessive dishing due to nonuniform Cu removal or nonuniform Cu plating. In addition, the particular aggressive slurry used in this study exhibited etching behavior during CMP which contributed to the nonuniform Cu removal. With this type of slurry both mechanical removal and chemical etching can aid in the removal of thick Cu layers, however, care must be taken to avoid overpolishing of metal layers.

Figure 4. 3-D optical profile surface image of isolated TWI after CMP process showing 5µm of dishing inside the via.

Figure 5. Digital photo of isolated through-wafer via after CMP.

#### **ACKNOWLEDGMENTS**

This project is supported by the DARPA MTO office and administered by SPAWAR SYSCEN/San Diego, CA under contract number N66001-01-C8034. The authors gratefully thank Micron Technology for the donation of the Strasbaugh CMP tool and related consumables. Special thanks to Fujimi Corporation for providing the slurries.

#### REFERENCES

- Burkett, S.L., et al., Advanced processing techniques for throughwafer interconnects. Journal of Vacuum Science Technology, 2004. B 22(1): p. 248-256.

- [2] Qiao, X., et al. Innovative CMP processing by Using Agrassive Cu slurries in Through-Wafer Interconnect Applications. in AVS. 2003. San Fransisco, CA.

- [3] Peterson, M.L., et al., Challenges of Electroplated Copper Film and Device Characteristics for Copper Slurry Design, in Semiconductor Fabtech. 1999. p. 283-287.