# Boise State University ScholarWorks

Materials Science and Engineering Faculty Publications and Presentations

Department of Materials Science and Engineering

6-1-2010

# Limitations of Poole–Frenkel Conduction in Bilayer HfO<sub>2</sub>/SiO<sub>2</sub> MOS Devices

Richard G. Southwick III Boise State University

Justin Reed Boise State University

Christopher Buu Boise State University

Ross Butler

Boise State University

Gennadi Bersuker SEMATECH

$See\ next\ page\ for\ additional\ authors$

©2010 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. DOI: 10.1109/tdmr.2009.2039215

| thors<br>chard G. Southwid<br>owlton | k III, Justin Reed, Christopher Buu, Ross Butler, Gennadi Bersuker, and William I |

|--------------------------------------|-----------------------------------------------------------------------------------|

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

|                                      |                                                                                   |

# Limitations of Poole–Frenkel Conduction in Bilayer HfO<sub>2</sub>/SiO<sub>2</sub> MOS Devices

Richard G. Southwick, III, *Student Member, IEEE*, Justin Reed, *Student Member, IEEE*, Christopher Buu, *Student Member, IEEE*, Ross Butler, *Student Member, IEEE*, Gennadi Bersuker, *Member, IEEE*, and William B. Knowlton, *Senior Member, IEEE*

Abstract—The gate leakage current of metal-oxidesemiconductors (MOSs) composed of hafnium oxide (HfO<sub>2</sub>) exhibits temperature dependence, which is usually attributed to the standard Poole-Frenkel (P-F) transport model. However, the reported magnitudes of the trap barrier height vary significantly. This paper explores the fundamental challenges associated with applying the P-F model to describe transport in HfO<sub>2</sub>/SiO<sub>2</sub> bilayers in n/p MOS field-effect transistors composed of 3- and 5-nm HfO<sub>2</sub> on 1.1-nm SiO<sub>2</sub> dielectric stacks. The extracted P-F trap barrier height is shown to be dependent on several variables including the following: the temperature range, method of calculating the electric field, electric-field range considered, and HfO2 thickness. P-F conduction provides a consistent description of the gate leakage current only within a limited range of the current values while failing to explain the temperature dependence of the 3-nm HfO<sub>2</sub> stacks for gate voltages of less than 1 V, leaving other possible temperature-dependent mechanisms to be explored.

Index Terms—Carrier transport, cryogenic, hafnium oxide (HfO<sub>2</sub>), high-k dielectric, metal-oxide-semiconductors (MOS), Poole-Frenkel (P-F).

# I. INTRODUCTION

T HE NEXT generation of metal-oxide-semiconductor (MOS) field-effect transistors (MOSFETs) requires an increase in gate-oxide capacitance (per unit area) that can no longer be accommodated by reduction in the thickness of the typical gate oxides. High dielectric constant (high-k) oxides have received considerable attention as a solution to reduce gate leakage current while increasing the gate-oxide capacitance. Hafnium oxide (HfO<sub>2</sub>) is the prime candidate for replacing silicon dioxide (SiO<sub>2</sub>) and has recently been introduced in production. One of the continued challenges in the use of HfO<sub>2</sub> is the strong temperature dependence of the leakage current as compared with that of SiO<sub>2</sub> [1].

Manuscript received October 7, 2009; revised December 1, 2009; accepted December 15, 2009. Date of publication December 28, 2009; date of current version June 4, 2010. This work was supported in part by the Idaho SBoE-HERC, by the Micron Ph.D. Fellowship, and by DARPA Contract N66001-01-C-80345 and NIH INBRE P20RR16454.

R. G. Southwick, III, J. Reed, C. Buu, and R. Butler are with the Department of Electrical and Computer Engineering, Boise State University, Boise, ID 83725 USA.

G. Bersuker is with SEMATECH, Austin, TX 78741 USA (e-mail: Gennadi. Bersuker@sematech.org).

W. B. Knowlton is with the Electrical and Computer Engineering and Materials Science and Engineering Departments, Boise State University, Boise, ID 83725 USA (e-mail: bknowlton@boisestate.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TDMR.2009.2039215

For high-temperature measurements (300 K to  $\sim$ 500 K), many studies of electron transport in HfO<sub>2</sub> have attributed the gate leakage current to the Poole–Frenkel (P–F) conduction mechanism of electrons in HfO<sub>2</sub> [2]–[5]. Although P–F emission is widely employed as an explanation of the temperature dependence of gate leakage current in HfO<sub>2</sub> (and high-k dielectrics, in general), significant discrepancies have arisen in the reported trap-energy barrier heights (e.g., 0.35 eV [2], 0.68 eV [6], 1.11–1.36 eV [7], and 1.5 eV [5]). While the inconsistencies in the reported barrier heights may be attributed to different growth methods, pre- and postgrowth processing, and device technologies used, this paper explores several fundamental challenges that are present in extracting trap-energy barriers in HfO<sub>2</sub> gate stacks based on using the standard P–F model.

This paper examines whether the standard P–F model can describe charge transport over a wide temperature range in HfO<sub>2</sub>/SiO<sub>2</sub> bilayer dielectric stacks (6 K–400 K). In this paper, P-F analysis is applied to data collected over a broad range of temperatures and stress-free voltages. Particular attention is given to the following: 1) the P-F derived trap-energy barrier height's dependence on HfO<sub>2</sub> thickness; 2) calculation of the electric field in the oxide layer in which P-F conduction is suspected to take place; and 3) whether P-F transport occurs at typical MOSFET use conditions. The analysis of the data from HfO<sub>2</sub>/SiO<sub>2</sub> bilayer dielectric stacks reveals that the P-F behavior only occurs at very narrow temperature and electricfield ranges. Ignoring these limitations may lead to a variety of reported trap-barrier-height values of which several are physically unfounded. Furthermore, the analysis shows a leakagecurrent thickness dependence, which is not consistent with the P–F model. It is also found that certain approximations used to calculate the electric field in the dielectric can lead to significant errors in the P–F analysis. The data further brings to light that the standard P-F conduction model is unsuitable at the use conditions for highly scaled high-k dielectrics in MOS devices. The presented evidence suggests that the P-F model may be insufficient to explain transport behavior in high-k dielectric stacks.

## II. P-F TRANSPORTATION MECHANISM

The standard P–F mechanism was initially defined in a short paper by Frenkel in 1938 [8]. Frenkel's paper describes how the electron trap barrier height  $(\phi)$  is reduced in the presence of an electric field  $(E_{\rm ox})$  by

$$\Delta q\phi = \beta \sqrt{E_{\rm ox}} \tag{1}$$

where the P–F constant  $\beta$  is given by [9]

$$\beta = \sqrt{\frac{q^3}{\pi \varepsilon_0 \varepsilon_r}} \tag{2}$$

and q,  $\varepsilon_0$ , and  $\varepsilon_r$  are the electron charge, permittivity of free space, and the high-frequency dielectric constant, respectively [10], [11]. The derivation of the energy-potential lowering effect (1) depends on the hydrogenic potential. That is, the standard P-F mechanism incorporates the concept of a hydrogenic impurity for which the ionization energy potential is determined using the effective mass approximation [12]–[14]. The hydrogenic impurity includes both a charged ion impurity and a charged trapped carrier, which interact with each other. In his model, Frenkel only considered electrons and donor traps [8]. However, in the effective-mass approximation, the difference between the hydrogenic ionization energy potential for an electron and hole is simply the effective mass of the respective carriers. Hence, there is no reason why the P-F model cannot be applied to holes as it is applied to electrons.

According to Frenkel, for trapping to occur, the impurity must be ionized in the nontrapped state and neutral in the trapped state [10]. Since Frenkel's publication, the literature contains numerous papers of assorted derivations of P-F conduction (e.g., [9]), applications to various materials, and discussions on its limitations (e.g., [14] and [15]). A widely accepted mathematical expression for the standard P-F conduction  $(J_{\rm FP})$  can be written as

$$J_{\rm FP} = CE_{\rm ox}e^{-\frac{q\phi - \beta\sqrt{E_{\rm ox}}}{\xi^{KT}}} \tag{3}$$

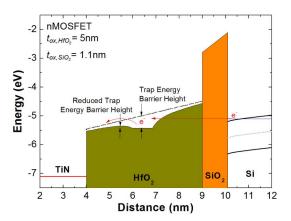

where C, K, T, and  $\xi$ , are a constant, Boltzmann's constant, temperature, and a factor that depends on acceptor compensation [11], [15], respectively. The value of  $\xi$  is usually between one and two. In Frenkel's original paper,  $\xi = 2$ . In much of the literature,  $\xi = 1$  (e.g., [6], [7], and [16]–[21]) which corresponds to heavily compensated traps [11]. The standard P-F conduction mechanism does not define how the traps are filled, only how they are emptied. The resulting P–F detrapping process is assumed to be the limiting step in the conduction mechanism. Traps are usually considered to be filled through quantum-mechanical tunneling [22]. An example depicting the P–F conduction path in HfO<sub>2</sub> with a SiO<sub>2</sub> interfacial layer (IL) is shown in Fig. 1.

Identifying the P–F transport can be achieved by constructing a P-F plot where (3) is linearized by plotting  $ln(J/E_{ox})$  versus  $E_{\rm ox}^{1/2}$ . If the P-F plot shows that the data are linear, P-F conduction is inferred. The slope of the line yields  $\beta/\xi KT$  from which the high-frequency dielectric constant can be extracted if  $\xi$  is known; however, usually it is assumed to be one. If C in (3) is known,  $\phi$  can be extracted from the y-intercept

$$\ln(C) - \frac{q\phi}{\xi KT}.$$

(4)

If C is not known, data from more than one temperature can be used to eliminate C.

Fig. 1. Simulated energy-band diagram showing the lowering of the trap potential barrier height in the presence of an electric field in HfO2 with a SiO<sub>2</sub> IL. The dashed line represents the conduction band in the HfO<sub>2</sub> without the trap. The diagram was created using [23], a  $\phi$  of 0.45 eV, and a relative high-frequency dielectric constant of 7.8; values extracted from the data and discussed in Section IV. The trap potential is located in the middle of the

An alternative approach to extracting  $\phi$  is achieved by following [6] and [18] in which (3) is linearized against the inverse of temperature as

$$\ln\left(\frac{J_{\rm FP}}{E_{\rm ox}}\right) = \ln(C) - \frac{q\phi - \beta\sqrt{E_{\rm ox}}}{\xi K} \frac{1}{T} \tag{5}$$

which predicts Arrhenius behavior. The slope of the resulting line is proportional to the reduced trap barrier height  $(\phi_r)$ ,  $q\phi - \beta E_{\rm ox}^{1/2}$ . Note that the reduced trap-energy barrier height decreases with increasing electric field. Extracting the slope in (5) at various electric fields yields  $\phi$  which can be found by extrapolating  $E_{\mathrm{ox}}^{1/2}$  to zero. This latter approach to finding  $\phi$  is the method used in this paper.

Regardless of the method utilized, the value of the electric field must be specific to the dielectric layer under consideration [1]. Calculating the electric field has been treated in various ways in the literature necessitating a discussion on how the electric-field calculation affects the extraction of  $\phi$ . Three common methods of calculating the electric field in a dual-dielectric layer stack (shown here for layers composed of HfO2 and SiO2) can be written in the form of (6) (e.g., [6] and [16]), (7) (e.g., [22]), and (8) (e.g., [19] and [24]) [1]

$$E_{\rm ox} = \frac{V_{\rm Gate} - V_{\rm FB}}{t_{\rm ox physical}} \tag{6}$$

$$E_{\text{ox}} = \frac{V_{\text{Gate}} - V_{\text{FB}}}{t_{\text{ox,physical}}}$$

(6)

$$E_{\text{ox,HfO}_2} = \frac{V_{\text{Gate}} - V_{\text{FB}}}{t_{\text{ox,HfO}_2}} \frac{C_{\text{ox,SiO}_2}}{C_{\text{ox,HfO}_2} + C_{\text{ox,SiO}_2}}$$

(7)

$$E_{\text{ox,HfO}_2} = \frac{V_{\text{Gate}} - V_{\text{FB}} - \phi_s(V_{\text{Gate}})}{t_{\text{ox,HfO}_2}} \frac{C_{\text{ox,SiO}_2}}{C_{\text{ox,HfO}_2} + C_{\text{ox,SiO}_2}}$$

(9)

$$E_{\text{ox,HfO}_2} = \frac{r_{\text{Gate}}}{t_{\text{ox,HfO}_2}} \frac{r_{\text{FB}} \varphi_s(r_{\text{Gate}})}{C_{\text{ox,HfO}_2} + C_{\text{ox,SiO}_2}}$$

(8)

where  $V_{\rm Gate}$ ,  $V_{\rm FB}$ ,  $t_{\rm ox}$ ,  $C_{\rm ox}$ , and  $\phi_s$  are the gate voltage, flatband voltage, oxide thickness, oxide capacitance, and surface potential in the semiconductor, respectively. Equation (6) treats the dual dielectric as a single dielectric. Equation (7) improves the electric-field calculation in the HfO2 by considering the mismatch in the dielectric constants. Equation (8) is a further refinement accounting for the potential drop in the silicon  $(\phi_s)$ .

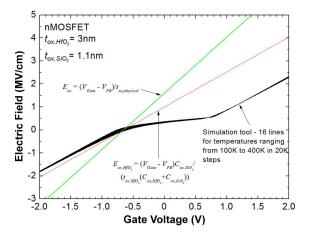

Fig. 2. Calculated electric field in a TiN/HfO $_2$ /SiO $_2$ /Si gate stack using (6) and (7) and [23] and [26] for (8). Simulations for temperatures ranging from 100 K to 400 K are shown [23]. After [1].

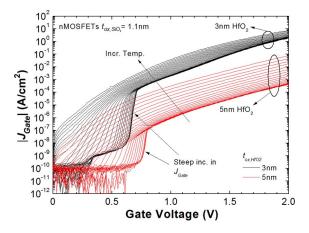

Fig. 3. Typical gate leakage currents for 3- and 5-nm  $HfO_2/SiO_2$  nMOSFETs. Significantly higher temperature dependence in 5-nm  $HfO_2/SiO_2$  gate leakage current is observed compared with the 3-nm  $HfO_2/SiO_2$ . A steep increase in the gate leakage current with respect to the gate voltage is observed near the threshold voltage.

The accuracy of (8) depends on the accuracy to which  $\phi_s$  is known. One method of reducing the error by accounting for the potential drop in the silicon is the use of simulation software (e.g., [23] and [25]) from which  $\phi_s$  or  $E_{\rm ox,HfO2}$  can be extracted. Fig. 2 shows a comparison of the calculated electric field using (6) and (7), and the Boise State University energy-band simulation tool to account for  $\phi_s$  [23], [26].

As observed in Fig. 2, there is a large difference between the calculated electric field using (6)–(8). As will be shown, the large difference in the calculated values of electric field using (6)–(8) has a substantial impact on the calculated  $\phi$ . Fig. 2 also shows the electric field in HfO<sub>2</sub> as a function of gate voltage for temperatures ranging from 100 K to 400 K as calculated by [23] and [26]. It has been shown that a minimal variation in the electric field occurs below 100 K [1]. The electric field shows little variation with temperature at the simulated doping concentration (2.5 × 10<sup>18</sup> cm<sup>-3</sup>). Because the electric field remains nominally unchanged with respect to temperature, the temperature dependence of  $\phi_s$  for highly doped substrates can be assumed constant. From this exercise, Fig. 2 shows that the use of the simplifying equations of (6) and (7) can lead to substantial error when calculating the electric field as compared with (8).

#### III. EXPERIMENTAL PROCEDURE

The devices used in this study are n/pMOSFETs fabricated using a standard CMOS process flow including a 10-s 1000-°C anneal for dopant activation and 480-°C forming-gas anneals. The gate stack of each MOSFET consists of a titanium nitride (TiN) metal gate and a dielectric bilayer of either 3 nm or 5 nm of HfO<sub>2</sub> grown by atomic layer deposition on a 1.1-nm chemically grown SiO<sub>2</sub> IL. A more detailed description of the fabrication process is presented in [27]. Control devices fabricated with a 2-nm SiO<sub>2</sub> gate dielectric are used for comparison. In order to increase the signal to noise ratio in the gate-leakagecurrent measurements, large MOSFETs of 30-μm/30-μm (width/length) and  $50-\mu \text{m}/50-\mu \text{m}$  dimensions were tested. A Janis Research custom-built variable-temperature probe station (5.6 K–450 K) with actively cooled Kelvin probes, to limit heat injection into the devices, was used for all measurements. A Keithley 4200SCS with remote preamps was interfaced with the variable-temperature probe station. Gate-leakage-current measurements were performed for the electron-substrate injection regime (positive gate biases). The electric-field calculations were performed using [23] and [26] and were calibrated using the flatband voltage and material parameters extracted using capacitance-voltage measurements in [27].

## IV. RESULTS AND DISCUSSION

Based on the P–F model, varying the thickness of the  $HfO_2$  in the  $HfO_2/SiO_2$  gate stack should not have an effect on the extracted trap-energy barrier height  $(\phi)$ . To test this model's prediction, the leakage current through the 3- and 5-nm thick  $HfO_2/SiO_2$  gate stack was examined as a function of applied voltage over a wide range of temperatures. Typical gate leakage currents for nMOSFETs composed of 3-nm  $HfO_2$  and 5-nm  $HfO_2$  for temperatures ranging from 6 K to 400 K are shown in Fig. 3 for electron-substrate injection. As expected, the gate-leakage-current density  $(J_{\rm Gate})$  for the 5-nm  $HfO_2$  stack is decades lower than the 3-nm  $HfO_2$  stack. For both nMOSFETs and pMOSFETs (not shown), the gate-leakage-current rate of increase with temperature is higher for the 5-nm  $HfO_2$  than for the 3-nm  $HfO_2$ .

Another intriguing aspect of Fig. 3 is the steep increase in the gate-current density with gate voltage near a gate bias of 0.5 V. For pMOSFETs (not shown), a corresponding steep increase in the gate leakage current is observed at negative polarities [1]. The steep decrease in gate leakage current at low gate biases is due to the decrease of minority carriers below the threshold voltage resulting in supply-limited transport [1]. Above the threshold voltage, the gate leakage current is dominated by the transport path through the dielectric, whether due to tunneling, defect-mediated tunneling, or some other transport mechanism [1].

Typically, P–F analysis is performed in the transport-path-limited region, as opposed to the supply-limited transport regime, of the gate-leakage-current plot (e.g., voltages above  $\sim\!0.7$  V in Fig. 3). Following the second method for calculating  $\phi$  described in Section II, a  $J_{\rm Gate}/E_{\rm ox,HfO2}$  P–F plot at various temperatures is shown in Fig. 4. For P–F transport to dominate according to (3), the data in Fig. 4 should be linear. Except for a small electric-field interval, the data in Fig. 4

Fig. 4. P–F plot of the gate leakage current of a 3-nm  $HfO_2$  1.1-nm  $SiO_2$  nMOSFET for temperatures ranging from 6 K to 400 K. Most temperatures are not plotted to increase clarity of the data.

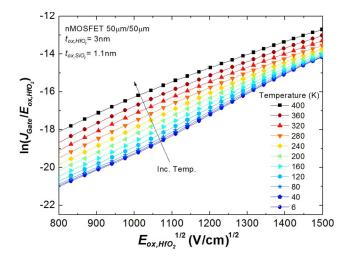

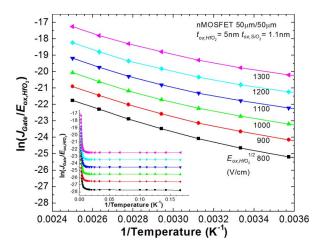

Fig. 5. Arrhenius P–F plot at various electric field strengths of a 5-nm  $HfO_2$  1.1-nm  $SiO_2$  nMOSFET for temperatures 280 K to 400 K. Inset plot is for temperatures 6 K to 400 K.

are not linear for the entire electric-field range shown [800 to 1550  $(V/cm)^{1/2}$ ]. To describe the nonlinear data in a P–F plot, a saturation P-F analysis approach has been proposed in [28] and developed in [15] and [29] whereby Fermi-Dirac statistics are used instead of Maxwell-Boltzmann. In classic P-F, below the saturation voltage, carriers are thermally ionized over the trap barrier. The presence of the electric field assists carriers in overcoming the trap barrier. For voltages at or above the saturation voltage, the trap barrier is reduced to zero, and the Coulombic traps have no effect on the carriers. Saturation P–F dominates when the conductivity  $(J_{\rm Gate}/E_{\rm ox,HfO2})$  for various temperatures approaches a crossing point, where temperature is not needed for the carrier to overcome the trap potential. However, in this paper, the conductivity data in Fig. 4 is not observed to cross or approach crossing indicating that the P-F saturation is not occurring. Therefore, saturation P–F analysis for the nonlinear data observed in Fig. 4 is not applicable.

To verify whether the P–F transport follows the Arrhenius-type behavior (5), the conductivity  $(J_{\rm Gate}/E_{\rm ox,HfO2})$  is plotted versus the inverse temperature at various electric fields

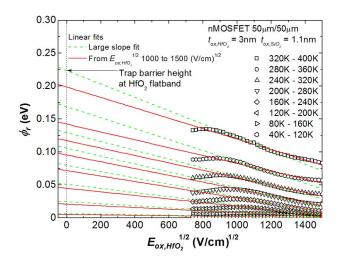

Fig. 6. Reduced trap barrier height  $(\phi_T)$  at various electric-field strengths using eight different temperature ranges from e.g., Fig. 5.  $\phi_T$  at flatband (vertical dashed line), or  $\phi$ , is determined by linear extrapolation, e.g., red (solid) and green (dashed) lines.

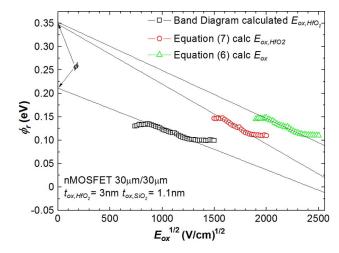

Fig. 7.  $\phi$  extraction using  $\phi_r$ 's extracted using the electric field calculated in three different ways. The black lines are linear best fit to the most linear segment of the data

as shown in Fig. 5. The inset of Fig. 5 displays the entire temperature range examined, whereas Fig. 5 only shows 280 K to 400 K. The entire temperature range shows a strong temperature-dependent region  $(T>200~{\rm K})$  and a weak temperature-sensitive region  $(T<50~{\rm K})$ . For the strong temperature-dependent regime,  $\phi_r$  at various electric-field strengths is extracted, assuming  $\xi=1$ , and plotted against the square root of the electric field, Fig. 6, in order to extract  $\phi$ . The data in Fig. 5 are not completely linear, and thus, the behavior is not standard P–F. The slope of the data is observed to increase with increasing temperature to the highest temperature (400 K) for which measurements were performed. Therefore,  $\phi_r$  extracted from the data will be dependent on the temperature range used as shown in Fig. 6.

Since the data in the Arrhenius P–F plot in Fig. 5 show a slight curvature with the slope increasing as temperature increases, it is evident that (5), obtained by linearizing (3), cannot be applied to the data. Equation (3) was derived assuming a single trap-energy level, hence, the data do not exhibit a single trap-energy-level behavior. The observed nonlinearity of the

data may stem from several possibilities. One possibility is that several series of linear data with dissimilar slopes (i.e., various trap-energy levels) may exist and combine to form nonlinear data. Another possible explanation may be that the wavefunctions of the traps overlap due to a high defect density. Overlapping of the wavefunctions would lead to the potentials of the traps to overlap which may broaden the distribution of trap-energy barrier heights  $(\phi$ 's) [30]. An additional possibility might be attributed to the presence of charged traps (not considered in P–F conduction) that are taking part in carrier transport which is indicative of multivalent traps.

Due to the curvature of the data, only a limited range of data can be analyzed and explained using the standard P–F model. This finding highlights two uncertainties with the P–F model. First, if the data are linear over only a narrow range of temperatures, the extracted  $\phi$  seems physically tenuous. Second, when a narrow range of temperatures is selected for analysis, then the temperatures outside the narrow temperature range are not being considered, thereby indicating that other  $\phi$ 's exist.

Regardless of the cause, the curvature in the data in Fig. 5 influences the extracted reduced trap-energy barrier height  $(\phi_r)$ depending on the temperature range used to perform the linear fit. Fig. 6 shows  $\phi_r$  extracted for a 3-nm HfO<sub>2</sub> on 1.1-nm SiO<sub>2</sub> nMOSFET using eight different temperature ranges. To obtain  $\phi$ ,  $\phi_r$  is extrapolated to  $E_{\text{ox,HfO2}} = 0$  shown by the dashed vertical line in Fig. 6. As shown in Fig. 6, the temperature range used for calculating  $\phi_r$ , as well as the range of electric-field strengths to perform the linear regression fit to extrapolate  $\phi$ , yields significantly different results. The green (dashed) lines in Fig. 6 correspond to extracting  $\phi$  using the slope of the  $\phi_r$ 's which would result in the greatest  $\phi$ . The red (solid) lines in Fig. 6 correspond to a linear fit using electric-field strengths ranging from 1000 to 1500 (V/cm)<sup>1/2</sup>. Both red and green lines illustrate the wide distribution of  $\phi$ 's that can be extracted. The standard P–F model predicts a constant slope for the data plotted in the manner of Fig. 6. The heterogeneity of the slope in Fig. 6 suggests that P–F conduction is not an appropriate model or is limited to a short electric-field range.

As was alluded to earlier, the method of calculating the electric field in the  $HfO_2$  also has significant effects on the extracted  $\phi$ . Fig. 7 shows the various  $\phi_r$ 's extracted using (6), (7), and [23] for calculating the electric field. The linear fits, for extrapolating  $\phi$ , were performed over the largest existing linear range which also resulted in the largest  $\phi$ . Using the simplified equations of (6) and (7) to calculate the  $HfO_2$  electric field results in an overestimation of  $\phi$  ( $\sim$ 0.35 eV) when compared with the electric field calculated by [23] ( $\sim$ 0.21 eV). Fig. 7 thus shows the importance the method of electric-field calculation has on the P–F  $\phi$ .

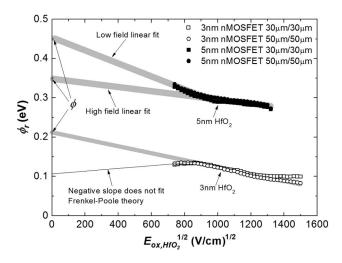

As was shown in Fig. 3, the temperature dependence of the 5-nm HfO $_2$  devices differed considerably from the 3-nm HfO $_2$  devices. This temperature-dependence difference is also observed in the P–F  $\phi$  extraction (Fig. 8). Fig. 8 shows the  $\phi_{r}$ 's for nMOSFETs with 5-nm HfO $_2$  and 3-nm HfO $_2$ . Similar values were obtained for pMOSFETs. The extracted  $\phi$  for the n/pMOSFETs composed of 5-nm HfO $_2$  is  $\sim$ 0.45 eV below the HfO $_2$  conduction band for a low electric-field fit and  $\sim$ 0.35 eV below for a high electric-field fit. The P–F analysis

Fig. 8. Electric-field dependence of the  $\phi_r$  (extracted from temperatures ranging from 320 K to 400 K) for the 5-nm HfO $_2$  and 3-nm HfO $_2$  nMOSFETs. The thick gray lines represent linear fits to the data. For the 5-nm HfO $_2$  devices, two linear regimes are observed and give different trap-energy barriers. The thin black linear-fit line for the 3-nm HfO $_2$  devices shows P–F conduction is not valid in the low-field regime as  $\phi_r$  increases with electric field instead of being reduced

for n/pMOSFETs composed of 3-nm HfO<sub>2</sub> results in a  $\phi$  of  $\sim$ 0.21 eV below the HfO<sub>2</sub> conduction band. Therefore, the HfO<sub>2</sub> thickness affects the measured  $\phi$ . The similarly calculated  $\phi$ 's for n and pMOSFETs verify that the same traps in the HfO<sub>2</sub> are responsible for the gate leakage current whether in nMOS or pMOS configuration and thereby independent of the silicon doping and related processing.

A reason for the thickness dependence of the calculated  $\phi$ may best be understood through Fig. 1. Fig. 1 shows the trap potential of a 0.45-eV trap-energy barrier with a relative highfrequency dielectric constant of 7.8 (a high value) located in the middle of the 5-nm HfO2 layer. The value of the trapenergy barrier was extrapolated from Fig. 8, while the highfrequency dielectric constant was extracted by calculating  $\beta$ from Fig. 4 using 400 K data and assuming  $\xi = 1$ . Because the P–F potential is based on the concept of a hydrogenic impurity, the Coulombic potential between the electron and positive trap, shown in Fig. 1, extends over a large distance that is comparable with the HfO<sub>2</sub> layer thickness. Depending on the location of the trap and thickness of the HfO<sub>2</sub>, standard P–F conduction may not dominate, and the resulting transport mechanism becomes thickness dependent. P-F analysis, shown in Fig. 8, indicates that the 3-nm  $HfO_2$  layer contains traps with lower  $\phi$ 's than the  $\phi$ 's extracted for the 5-nm HfO<sub>2</sub>. For the high-field regime, the difference observed in  $\phi$ 's between the 3- and 5-nm HfO<sub>2</sub> may result from the large delocalized trap potential (Fig. 1) assumed by the P-F model via an effective-mass approximation. A large delocalized trap potential similar in diameter to the thickness of the HfO<sub>2</sub> may reduce  $\phi$  to more than what is predicted in (1). This supposition assumes that P–F conduction is prevalent. Conversely, the differences in observed  $\phi$ 's between the 3- and 5-nm HfO<sub>2</sub> may be due to the presence of another carriertransport mechanism. Regardless of the possible explanations to describe the observed differences, the P-F model does not consider a dielectric-thickness dependence and thus, is inadequate to explain the differences observed in Fig. 8.

For the 3-nm HfO<sub>2</sub> devices shown in Figs. 6 and 8,  $\phi_r$  for electric fields between ~700 and ~900 (V/cm)<sup>1/2</sup> increases with increasing field strength. If the governing carrier-transport mechanism is P–F conduction,  $\phi_r$  should decrease rather then increase with increasing electric field according to (1). Hence, for the 3-nm HfO<sub>2</sub> devices in this paper, it is evident that the P–F transport does not explain the temperature dependence of the gate-leakage-current density for electric-field strengths below ~900 (V/cm)<sup>1/2</sup> or gate voltages below 1 V. Consequently, for typical MOSFET operation conditions, ( $V_{\rm Gate} < \sim$ 1 V), P–F transport is not dominant in 3-nm HfO<sub>2</sub>, and a different thermally activated carrier-transport mechanism dominates. This finding agrees with similar findings in [1].

#### V. CONCLUSION

Standard P–F analysis (3) has been applied to metal-electrode high-k gate stacks composed of 3- or 5-nm HfO $_2$  on 1.1-nm SiO $_2$ . Resulting trap barrier heights ( $\phi$ 's) ranged from 0.21 eV below the HfO $_2$  conduction band for the 3-nm HfO $_2$  sample to 0.45 eV for the 5-nm HfO $_2$  sample ( $T=320~\mathrm{K}$ –400 K).

In this paper, a much broader temperature range (6 K–400 K) than is typical (room temperature to  $\sim$ 400 K) was examined. Evidence indicating that the data do not conform to the P–F framework was determined and is summarized as follows.

- 1) When implementing standard P–F analysis to extract  $\phi$  from the data, it was found out that the extracted  $\phi$  depends on the temperature range selected (Fig. 6). The standard P–F model predicts monoenergetic trap levels, so  $\phi$  should not vary with temperature.

- 2) Thicker  $HfO_2$  samples resulted in larger  $\phi$ 's than thin  $HfO_2$  samples, resulting in a thickness dependence. The standard P-F model does not predict thickness dependence in the leakage current.

- 3) For 3-nm HfO<sub>2</sub> MOSFETs, P–F transport could not explain the transport-mechanism trend for gate voltages of less than 1 V. As the device voltage operating regime is in this regime, ~1 V and less, the dominant leakage-current mechanism is not explained by the standard P–F analysis.

The standard P–F model as applied to the high-k dielectrics assumes that the role of defects in the  $\mathrm{SiO}_2$  (or high- $k/\mathrm{SiO}_2$  interface) in the temperature dependence of the gate leakage current are negligible. Defects in the IL have been shown to have important implications in the stress-induced leakage current [31]. Since defects in the IL have been shown to have a significant influence in the gate leakage current at room temperature, their effects should be considered in describing the temperature dependence of the gate leakage current.

In summary, not only may the different  $\phi$ 's reported using P–F conduction in the literature be dependent on device and processing parameters but they may also depend on the temperature range tested, method of electric-field calculation, chosen electric-field range for the  $\phi$  extraction, and HfO<sub>2</sub> thickness. Consequently, the standard P–F model may only be capable of explaining a narrow range of the gate leakage current in HfO<sub>2</sub> dielectrics. Although beyond the scope of this paper, additional studies are required to identify other possible temperature-

dependent conduction mechanisms that describe the data. One potential approach is to include atomic-level properties of the involved defects in the high-k and IL that include lattice-relaxation effects [31].

## ACKNOWLEDGMENT

The authors would like to thank Dr. A. Moll for her candid input, and the contributions of fellow members of the Knowlton Research Group at Boise State University.

# REFERENCES

- [1] R. G. Southwick, III, J. Reed, C. Buu, H. Bui, R. Butler, G. Bersuker, and W. B. Knowlton, "Temperature (5.6–300 K) dependence comparison of carrier transport mechanisms in HfO<sub>2</sub>/SiO<sub>2</sub> and SiO<sub>2</sub> MOS gate stacks," in *Proc. Int. Integr. Rel. Workshop Final Report*, 2008, pp. 48–54.

- [2] G. Ribes, S. Bruyere, D. Roy, C. Parthasarthy, M. Muller, M. Denais, V. Huard, T. Skotnicki, and G. Ghibaudo, "Physical origin of Vt instabilities in high-k dielectrics and process optimisation," in *Proc. IEEE Int. Integr. Rel. Workshop Final Report*, 2005, pp. 75–78.

- [3] G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, and G. Ghibaudo, "Review on high-k dielectric reliability issues," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 1, pp. 5–19, Mar. 2005.

- [4] W. Zhu, T. P. Ma, T. Tamagawa, Y. Di, J. Kim, R. Carruthers, M. Gibson, and T. Furukawa, "HfO<sub>2</sub> and HfAlO for CMOS: Thermal stability and current transport," in *IEDM Tech. Dig.*, 2001, pp. 20.4.1–20.4.4.

- [5] W. J. Zhu, T.-P. Ma, T. Tamagawa, J. Kim, and Y. Di, "Current transport in metal/hafnium oxide/silicon structure," *IEEE Electron Device Lett.*, vol. 23, no. 2, pp. 97–99, Feb. 2002.

- [6] T. P. Ma, H. M. Bu, X. W. Wang, L. Y. Song, W. He, and M. M. Wang, "Special reliability features for Hf-based high-k gate dielectrics," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 1, pp. 36–44, Mar. 2005.

- [7] S. Pan, S.-J. Ding, Y. Huang, Y.-J. Huang, D. W. Zhang, L.-K. Wang, and R. Liu, "High-temperature conduction behaviors of HfO<sub>2</sub>/TaN-based metal-insulator-metal capacitors," *J. Appl. Phys.*, vol. 102, no. 7, p. 073 706-5, Oct. 2007.

- [8] J. Frenkel, "On pre-breakdown phenomena in insulators and electronic semi-conductors," *Phys. Rev.*, vol. 54, no. 8, pp. 647–648, Oct. 1938.

- [9] R. M. Hill, "Poole–Frenkel conduction in amorphous solids," *Philos. Mag.*, vol. 23, no. 181, pp. 59–86, Jan. 1971.

- [10] J. G. Simmons, "Poole–Frenkel effect and Schotky effect in metalinsulator–metal systems," *Phys. Rev.*, vol. 155, no. 3, pp. 657–660, Mar. 1967.

- [11] J. R. Yeargan and H. L. Taylor, "The Poole–Frenkel effect with compensation present," *J. Appl. Phys.*, vol. 39, no. 12, pp. 5600–5604, Nov. 1968.

- [12] P. Y. Yu and M. Cardona, Fundamentals of Semiconductors—Physics and Material Properties. Berlin, Germany: Springer-Verlag, 1996, pp. 152–157.

- [13] A. Hayes and A. M. Stoneham, Defects and Defect Processes in Nonmetallic Solids. New York: Wiley, 1985.

- [14] A. K. Jonscher, "Electronic properties of amorphous dielectric films," Thin Solid Films, vol. 1, no. 3, pp. 213–234, 1967.

- [15] W. R. Harrell and J. Frey, "Observation of Poole–Frenkel effect saturation in SiO<sub>2</sub> and other insulating films," *Thin Solid Films*, vol. 352, no. 1/2, pp. 195–204, Sep. 1999.

- [16] K. Y. Cheong, J. H. Moon, H. J. Kim, W. Bahng, and N.-K. Kim, "Current conduction mechanisms in atomic-layer-deposited HfO<sub>2</sub>/nitrided SiO<sub>2</sub> stacked gate on 4H silicon carbide," *J. Appl. Phys.*, vol. 103, no. 8, p. 084 113-8, Apr. 2008.

- [17] H. W. Chen, S. Y. Chen, K. C. Chen, H. S. Huang, C. H. Liu, F. C. Chiu, K. W. Liu, K. C. Lin, L. W. Cheng, C. T. Lin, G. H. Ma, and S. W. Sun, "Electrical characterization and carrier transportation in Hf-silicate dielectrics using ALD gate stacks for 90-nm node MOSFETs," *Appl. Surf. Sci.*, vol. 254, no. 19, pp. 6127–6130, Jul. 2008.

- [18] C.-C. Yeh, T. P. Ma, N. Ramaswamy, N. Rocklein, D. Gealy, T. Graettinger, and K. Min, "Frenkel–Poole trap energy extraction of atomic layer deposited Al<sub>2</sub>O<sub>3</sub> and Hf<sub>x</sub>Al<sub>y</sub>O thin films," *Appl. Phys. Lett.*, vol. 91, no. 11, p. 113 521-3, Sep. 2007.

- [19] I. Z. Mitrovic, Y. Lu, O. Buiu, and S. Hall, "Current transport mechanisms in (HfO<sub>2</sub>)<sub>x</sub>(SiO<sub>2</sub>)<sub>1-x</sub>/SiO<sub>2</sub> gate stacks," *Microelectron. Eng.*, vol. 84, no. 9/10, pp. 2306–2309, Sep./Oct. 2007.

- [20] Y. Lu, O. Buiu, S. Hall, I. Z. Mitrovic, W. Davey, R. J. Potter, and P. R. Chalker, "Tuneable electrical properties of hafnium aluminate gate dielectrics deposited by metal organic chemical vapour deposition,"

- Microelectron. Rel., vol. 47, no. 4/5, pp. 722–725, Apr./May 2007.

[21] Y. Lu, O. Buiu, S. Hall, and P. K. Hurley, "Optical and electrical characterization of hafnium oxide deposited by MOCVD," Microelectron. Reliab., vol. 45, no. 5/6, pp. 965-968, May/Jun. 2005.

- [22] D. S. Jeong, H. B. Park, and C. S. Hwang, "Reasons for obtaining an optical dielectric constant from the Poole-Frenkel conduction behavior of atomic-layer-deposited HfO2 films," Appl. Phys. Lett., vol. 86, no. 7, p. 072 903-3, Feb. 2005.

- [23] R. G. Southwick and W. B. Knowlton, "Stacked dual oxide MOS energy band diagram visual representation program (IRW student paper)," IEEE Trans. Device Mater. Rel., vol. 6, no. 2, pp. 136-145, Jun. 2006.

- [24] J. C. Tinoco, M. Estrada, B. Iñiguez, and A. Cerdeira, "Conduction mechanisms of silicon oxide/titanium oxide MOS stack structures,' Microelectron. Rel., vol. 48, no. 3, pp. 370-381, Mar. 2008.

- [25] SILVACO Webpage. [Online]. Available: http://www.silvaco.com/

- [26] Boise State University Energy Band Diagram Program Webpage. [Online]. Available: http://coen.boisestate.edu/bknowlton/research/

- G. Bersuker, J. Peterson, J. Barnett, A. Korkin, J. H. Sim, R. Choi, B. H. Lee, J. Greer, P. Lysaght, and H. R. Huff, "Properties of the interfacial layer in the high-k gate stack and transistor performance," in *Proc.* ECS Spring Meeting, 2005, pp. 141–145.

[28] R. Ongaro and A. Pillonnet, "Poole–Frenkel (PF) effect high field satura-

- tion," Rev. Phys. Appl., vol. 24, no. 12, pp. 1085-1095, 1989.

- W. R. Harrell, T. H. Cordella, and K. F. Poole, "Implications of non-linear Poole-Frenkel plots on high-k dielectric leakage," ECS Trans., vol. 1, no. 5, pp. 705-716, Oct. 2006.

- [30] N. F. Mott, "Metal-insulator transition," Rev. Mod. Phys., vol. 40, no. 4, pp. 677-683, Oct. 1968.

- [31] G. Bersuker, D. Heh, C. Young, H. Park, P. Khanal, L. Larcher, A. Padovani, P. Lenahan, J. Ryan, B. H. Lee, H. Tseng, and R. Jammy, "Breakdown in the metal/high-k gate stack: Identifying the "weak link" in the multilayer dielectric," in IEDM Tech. Dig., 2008, pp. 1-4.

Richard G. Southwick, III (S'04) was born in Cedar City, UT, in 1981. He received the B.S. and M.S. degrees in electrical engineering from Boise State University, Boise, ID, in 2004 and 2008, respectively, where he is currently working toward the Ph.D. degree in electrical engineering.

His research interests include gate-oxide reliability studies and alternative gate-oxide dielectrics.

Mr. Southwick has served on the organizing committee for the IEEE International Integrated Reliability Workshop from 2009 up to the present.

Justin Reed (S'08) received the B.S. degree in electrical and computer engineering from Boise State University, Boise, ID, in 2009.

He has been an undergraduate Research Assistant for Dr. Knowlton since 2006 with Boise State University, studying high-k dielectrics and other materials through low-temperature measurements.

area is dielectrophoresis.

Christopher Buu (S'07) was born in Boise, ID, on January 17, 1987. He received the B.S. degree in electrical and computer engineering from Boise State University, Boise, ID, in 2009, where he is currently working toward the M.S. degree in electrical and computer engineering.

He has been with Boise State University since he joined Dr. Knowlton's research group in 2006 as an Undergraduate Research Assistant, with a research in MOS device characterization. In 2009, he became a Graduate Research Assistant and his current research

Ross Butler (S'09) is currently working toward the B.S. degree in electrical and computer engineering with focus on embedded system design, at Boise State University, Boise, ID.

His professional career in software development began in 1980. Prior to becoming a full-time student in 2007, he was a Senior Software Engineer with Micron Technologies, Inc., Boise, where he specialized in statistical process control software design and development. He currently works part time as an undergraduate Research Assistant in Dr. Knowlton's

research group with Boise State University. His research interests include characterization of charge trapping in novel dielectric materials and automation of complex experimental procedures.

Gennadi Bersuker (M'05) received the M.S. degree in physics from Leningrad State University, St. Petersburg, Russia, and the Ph.D. degree in physics from Kishinev State University, Kishinev, Moldova.

After graduation, he was with Moldavian Academy of Sciences, and then worked with Leiden University and with the University of Texas at Austin. Since 1994, he has with SEMATECH, Austin, TX, working on process-induced charging damage, electrical characterization of Cu/low- $\kappa$  interconnect,

high- $\kappa$  gate stacks, and advanced CMOS process development. He has over 200 publications on the electronic properties of dielectrics and semiconductor characterization and reliability.

Dr. Bersuker is a SEMATECH Fellow.

William B. Knowlton (M'00-SM'09) was born in Sewart Air Force Base, TN, on June 15, 1960. He received the B.S., M.S., and Ph.D. degrees in materials science and engineering from the University of California, Berkeley, in 1992, 1995, and 1998, respectively. His doctoral work included the study of point defects and modeling diffusion in silicon and the development, fabrication, characterization of dark-matter particle detectors, X-ray detectors, and far-infrared resonant detectors.

In 1997, he was with Hewlett Packard Laborato-

ries where he studied dislocations and structural properties in heteroepitaxial grown thin film and bulk-grown GaN material systems to optimize light output in LEDs. He was with Insight Analytical Laboratories in 1998 where he consulted and performed electromigration and dielectric reliability studies. Since 2000, he has been with the faculty, Electrical and Computer Engineering, Boise State University, Boise, ID. He has codeveloped five new programs and a department in Materials Science and Engineering where he is the Program Coordinator for Graduate Studies and holds a joint appointment. He has published over 60 papers in peer-reviewed journals and conferences. His research activities include biomolecular electronic devices, MOS device, and simple circuit reliability physics, materials characterization, nanofabrication of materials, and through wafer interconnects.

Prof. Knowlton is the recipient of several teaching and research awards including the 2004 and 2008 Boise State University Top Ten Scholar/Alumni Association Honored Faculty Member Awards, 2007 College of Engineering Professor of the Year Award, 2004 IEEE Student Chapter Electrical and Computer Engineering Professor of the Year Award, and the 2004 Boise State University Presidential Research and Scholarship Award. He is a member of the Materials Research Society and the American Physical Society. He has served on the organizing committees for the IEEE International Integrated Reliability Workshop from 2002 to 2005 and 2008 to the present, and the 2009 IEEE International Semiconductor Device Symposium, and was a Guest Editor for IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY in 2006 and 2008.